I, Brian Toth, hereby certify that the following document is, to the best of my knowledge and belief, a true and accurate translation from Japanese into English.

*JPH0794419 (Watanabe)*

I declare under the penalty of perjury under the laws of the United States of America that the foregoing is true and correct.

Signature

10/19/18

Date

Brian Toth

Name

**ASM Ex. 1006**

IPR Petition - USP 7,033,937

(19) Japan Patent Office (JP)

(12) **Japanese Unexamined Patent Application Publication (A)**

(11) Japanese Unexamined Patent Application Publication Number

**H7-94419**

(43) Publication date: April 7, 1995

| (51) Int. Cl. <sup>6</sup>      | Identification codes | JPO file numbers | FI                    | Technical indications |

|---------------------------------|----------------------|------------------|-----------------------|-----------------------|

| <b>H 01 L 21/205</b><br>21/3065 |                      |                  | <b>H 01 L 21/ 302</b> | <b>B</b>              |

Request for examination: Not yet requested Number of claims: 15 OL (Total of 15 pages)

|                          |                                       |                |                                                                                                                                     |

|--------------------------|---------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------|

| (21) Application number  | Japanese Patent Application H5-232994 | (71) Applicant | 000005108<br>Hitachi, Ltd.<br>4-6 Kanda-Surugadai, Chiyoda-ku, Tokyo-to                                                             |

| (22) Date of application | September 20, 1993                    | (72) Inventor  | Tomoji WATANABE<br>% Mechanical Engineering Research Laboratory,<br>Hitachi, Ltd., 502 Kandatsu-cho, Tsuchiura-shi,<br>Ibaraki-ken  |

|                          |                                       | (72) Inventor  | Shigeki HIRASAWA<br>% Mechanical Engineering Research Laboratory,<br>Hitachi, Ltd., 502 Kandatsu-cho, Tsuchiura-shi,<br>Ibaraki-ken |

|                          |                                       | (72) Inventor  | Nobuyuki MISE<br>% Mechanical Engineering Research Laboratory,<br>Hitachi, Ltd., 502 Kandatsu-cho, Tsuchiura-shi,<br>Ibaraki-ken    |

|                          |                                       | (74) Agent     | Patent Attorney Tatsuyuki UNUMA                                                                                                     |

|                          |                                       |                | Continued on the last page                                                                                                          |

**(54) (TITLE OF THE INVENTION) SEMICONDUCTOR PROCESSING DEVICE**

**(57) (ABSTRACT)**

(PURPOSE) To enable a film forming device or an etching device to perform uniform processing with high reproducibility.

(CONSTITUTION) A film forming device is provided with a flat reaction tube 2 in a heating space formed by two parallel plate heaters 1, and a rectangular support plate 8 which supports a wafer 3 to be processed and is larger than the wafer 3 is disposed inside the heating space. A gas supply port 4 and a discharge port 5 are respectively provided at both ends of the reaction tube 2 so that the flow direction of a gas flowing through the reaction tube 2 can be switched.

(SCOPE OF THE PATENT CLAIMS)

(CLAIM 1) A semiconductor processing device for performing thin film formation or epitaxial growth on a wafer surface by housing a reaction tube inside a heating furnace, housing and heating a semiconductor wafer inside the reaction tube, and supplying a gas while discharging the gas from inside the reaction tube; wherein the heating furnace and the reaction tube have a roughly flat shape; and the reaction tube simultaneously holds and processes one or two wafers roughly horizontally.

(CLAIM 2) The semiconductor processing device according to Claim 1, wherein the reaction tube is made of quartz.

(CLAIM 3) The semiconductor processing device according to Claim 2, wherein a reinforcing member is provided inside, outside, or both inside and outside the reaction tube.

(CLAIM 4) The semiconductor processing device according to Claim 3, wherein the reinforcing member is fixed to the reaction tube by welding.

(CLAIM 5) The semiconductor processing device according to Claim 1, wherein the heating furnace is divided into a plurality of parallel plate heaters disposed roughly parallel to a processed surface of a wafer in a vertical direction of the wafer to be processed; and the parallel plate heaters are divided into a single central heater and a plurality of peripheral heaters surrounding the central heater.

(CLAIM 6) The semiconductor processing device according to Claim 1, comprising a means for changing a set temperature of the heating furnace during a single processing cycle of a wafer or for each cycle.

(CLAIM 7) A semiconductor processing device for performing thin film formation or epitaxial growth on a wafer surface by housing a reaction tube inside a heating furnace, housing and heating a semiconductor wafer inside the reaction tube, and supplying a gas while discharging the gas from inside the reaction tube; wherein the heating furnace is divided into at least two components.

(CLAIM 8) A semiconductor processing device for performing thin film formation, epitaxial growth, or etching on a wafer surface by housing a wafer inside a reaction chamber, supplying a gas while discharging the gas from inside the reaction chamber, and heating or cooling the housed wafer; wherein the reaction chamber has at least two openings at positions opposite one another so as to sandwich the housed wafer; each opening includes a gas supply port and a discharge port; the gas supply port and the discharge port are respectively connected to a gas source and a vacuum pump via a valve; and a structure of the reaction chamber including a wafer heating means or cooling means and a position of the wafer are roughly symmetrical with respect to a plane orthogonal to a line positioned in the center of the reaction chamber and connecting the two openings.

(CLAIM 9) The semiconductor processing device according to Claim 8, wherein the gas supply port and discharge port connected to the same opening are disposed in close proximity to one another so that most of the gas supplied from the gas supply port flows

directly out to the discharge port without passing through the reaction chamber.

(CLAIM 10) The semiconductor processing device according to Claim 8, comprising a means for switching a flow direction of the gas inside the reaction chamber during processing.

(CLAIM 11) The semiconductor processing device according to Claim 10, wherein when switching the flow of the gas, the means for switching the flow direction of the gas inside the reaction chamber first gradually switches the discharge port from the discharge port of one opening to the discharge port of another opening, and then gradually switches the gas supply port from the gas supply port of the other opening to the gas supply port of the first opening.

(CLAIM 12) The semiconductor processing device according to Claim 10 or 11, wherein when switching the flow direction of the gas during processing, the means for switching the flow direction of the gas inside the reaction chamber controls a gas flow volume and discharge rate so as to maintain a constant pressure inside the reaction chamber.

(CLAIM 13) The semiconductor processing device according to any one of Claims 1 to 12, wherein a gas introduced into the reaction chamber flows roughly parallel to a processed surface of the wafer.

(CLAIM 14) The semiconductor processing device according to any one of Claims 1 to 13, wherein a support plate for holding a wafer is disposed inside the reaction chamber; the support plate being roughly rectangular, and each edge of the support plate being larger than at least a diameter of the housed wafer.

(CLAIM 15) An LSI fabricated by forming a polysilicon film or phosphorus-doped polysilicon film for gate electrode wiring, a phosphorus glass film for an interlayer insulating film, and an  $\text{Si}_3\text{N}_4$  film for a capacitor insulating film using the semiconductor processing device according to any one of Claims 1 to 14.

(DETAILED DESCRIPTION OF THE INVENTION)

(0001)

(FIELD OF INDUSTRIAL APPLICATION) The present invention relates to a semiconductor processing device such as a thermal CVD device for forming a thin film such as a metal film, a metal silicide film, an oxide film, a nitride film, or a silicon film doped with impurities or the like on a wafer substrate surface, a plasma CVD device, an epitaxial growth device for growing a monocrystal layer on a wafer substrate, or a dry etching device for etching a thin film into a prescribed pattern. More particularly, the present invention relates to a semiconductor processing device designed while taking into consideration gas supply and wafer heating.

(0002)

(PRIOR ART) The thickness or characteristics of thin films and epitaxial growth layers formed by thermal CVD or plasma CVD depend largely on the temperature of the wafer or the reaction chamber and the concentration of gases (raw material gas, reaction products, intermediates, radicals, and the like). In addition, in dry etching, the concentration of radicals or reaction products obtained by decomposing the etching gas with plasma has a substantial

effect on the etching speed. Therefore, the uniformization of wafer temperature and the uniformization of gas concentration are critical issues for these processes. Conventional technology will be described hereinafter with primary focus on thermal CVD devices. (0003) Thermal CVD devices are broadly divided into batch-type and sheet-type devices. A batch-type vertical CVD device is a hot-wall type device (device in which the entire wall surface of the reaction chamber assumes a high temperature) for producing a film by inserting multiple wafers supported horizontally into a reaction tube provided inside a vertical cylindrical heating furnace and supplying a gas. Since the gas is ordinarily supplied from the bottom of the reaction tube, the reaction progresses and the gas concentration changes while the gas flows upward, and a difference in film thickness arises between the upper and lower wafers, so the effects of this difference are corrected by establishing a temperature gradient in the heating furnace. In addition, Japanese Unexamined Patent Application Publication H4-343412, for example, discloses technology configured to switch the flow direction of a gas that had been flowing from bottom to top to a direction from top to bottom inside a reaction chamber during film formation, and Japanese Unexamined Patent Application Publication S63-8299 discloses technology for holding and processing a wafer vertically inside a heating furnace consisting of parallel plate heaters. Further, Japanese Unexamined Patent Application Publication S63-232422 discloses a dispersion device configured to heat a wafer inserted horizontally into a vertical cylindrical furnace.

(0004) A sheet-type thermal CVD device is a cold-wall type device for producing a film by heating a wafer directly with a lamp or heating a wafer by placing the wafer on a susceptor heated with a heater, a lamp, or the like and then supplying a gas. In contrast to a batch-type device, there is no variation in film thickness between wafers due to changes in the gas concentration, but to reduce the film thickness distribution within the wafer plane, a method of rotating the wafer or supplying the gas in the form of a shower from above the wafer has been used. In addition, Japanese Unexamined Patent Application Publication H4-255214, for example, discloses technology configured to make the wafer temperature uniform by creatively designing the shapes and arrangement of heating lamps.

(0005) A plasma CVD device has basically the same structure as a susceptor-heated thermal CVD device and is further provided with an upper electrode for generating plasma. Gas supply methods include a method of supplying gas toward the center of a wafer from a plurality of inlets provided in the side walls of the reaction chamber, and a method of providing multiple small holes in the upper electrode and supplying gas in the form of a shower from the holes. In addition, Japanese Unexamined Patent Application Publication S63-102312 discloses technology for preventing fluctuations in wafer temperature by supplying He gas at a constant pressure between a wafer and a susceptor.

(0006) Dry etching devices are broadly divided into parallel plate type plasma etching devices and microwave etching devices. A parallel plate type plasma etching device is a device in which the wafer heating mechanism of a plasma CVD device is replaced with a cooling device, and only the gas that is supplied differs. A microwave etching device is configured by removing the upper electrode from a parallel plate type plasma etching device and providing a wave guide for introducing microwaves from this position. The etching gas is often supplied toward the center of a wafer from a plurality of inlets provided in the side surfaces of the etching chamber.

(0007)

(PROBLEMS TO BE SOLVED BY THE INVENTION) The devices of these conventional technologies had the following such problems.

(0008) In a batch-type vertical CVD device, the method of reducing variation in film thickness between wafers by establishing a temperature gradient inside the heating furnace requires an operation of finding an optimum furnace internal temperature distribution by repeated trial and error, and there are some cases in which a sufficiently satisfactory temperature distribution cannot be achieved by ordinary heater division (four zones in a current device). To solve this problem, a method of switching the flow of gas to the reverse direction during film formation (see Japanese Unexamined Patent Application Publication H4-343412) has been proposed, but since the structure of the heating furnace and reaction tube, the positions of wafers, and the like are not symmetrical with respect to the gas flow, it is difficult to sufficiently reduce variation in film thickness between upper and lower wafers by simply switching the gas.

(0009) In a cold-wall type sheet-type thermal CVD device (using both lamp heating and susceptor heating), it is necessary to set the temperature of the heat source to a very high level with respect to the wafer (thermal nonequilibrium state), and when the wafer emissivity changes (when the characteristics with respect to wavelength change due to differences in the type, thickness, or impurity concentration of the film formed on the surface), there is a problem in that the temperature reproducibility becomes poor. To solve this problem, a method of controlling the amount of heating by directly measuring the wafer temperature using a radiation thermometer has been proposed, but since the emissivity changes due to the formation of a film on the wafer surface, substantial measurement error arises, so the method is not practical. Further, in the case of susceptor heating, heat is transmitted from a susceptor to a wafer via an interposed gas, so the amount of heat transferred changes due to gaps or the like between the wafer and the susceptor, which is problematic in that the wafer temperature changes. To solve this problem, a method of supplying He gas at a constant pressure between the wafer and the susceptor (see Japanese Unexamined Patent Application Publication S63-102312) has been proposed, but the periphery must be pressed down so that the wafer does not rise upward, which leads to a problem in that the temperature in the vicinity of the wafer drops. In addition, device that uses lamp heating or susceptor heating has a problem in that the power consumption is large. In contrast, a device configured to insert and heat a wafer held vertically inside a vertical square furnace (see Japanese Unexamined Patent Application Publication S63-8299) and a device configured to insert and heat a wafer horizontally inside a vertical cylindrical furnace (see Japanese Unexamined Patent Application Publication S63-232422) have been proposed as devices which eliminate the drawbacks of a cold-wall type device (both of these devices are hot-wall type devices). However, since the quartz jig used to support the wafer is difficult to heat, the increase in temperature of portions to which the jig comes into contact within the wafer plane becomes slow, which is problematic in that the temperature uniformity becomes poor. Further, it is difficult to accommodate multiple chambers due to problems with handling.

(0010) In a method of supplying a gas toward the center of a wafer from a plurality of inlets in the side wall of a reaction

chamber in a plasma CVD device or a dry etching device, reaction products or the like tend to accumulate in the center of the wafer, which tends to cause unevenness in film thickness or etching speed. On the other hand, in a device configured to supply gas in the form of a shower from holes in an upper electrode, plasma is sometimes discharged abnormally in the vicinity of the holes. In addition, reaction products tend to adhere to the vicinity of the holes, which is problematic in that it causes the generation of foreign matter.

(0011) An object of the present invention is to enable a film forming device or an etching device to perform uniform processing with high reproducibility by providing a device structure in which a uniform gas concentration, a uniform wafer temperature, and temperature reproducibility are achieved.

(0012)

(MEANS FOR SOLVING THE PROBLEMS) The object described above is achieved by realizing a hot-wall type sheet-type device using resistance heating in a thermal CVD device. Specifically, the object is achieved by forming a heating furnace into a flat shape, placing a similarly flat reaction vessel into the heating furnace, inserting one or two wafers into the reaction vessel horizontally and heating the wafers, and supplying a gas into the reaction vessel to deposit a film on the wafer surface. Further, the object is achieved by placing a wafer on a rectangular support plate and processing the wafer, wherein each edge of the support plate is larger than the wafer diameter. In addition, the object is achieved by providing at least two openings in a reaction vessel, providing at least two sets of gas supply ports and discharge ports in the openings, and switching the flow of gas during film formation to form a film.

(0013) On the other hand, the object is achieved by providing at least two sets of gas supply ports and discharge ports in the reaction chamber of a plasma CVD device or a dry etching device, and advancing processing by switching the flow direction of gas during film formation or etching so that the supplied gas flows in one direction over the wafer.

(0014)

(OPERATION) In a thermal CVD device:

- Since the device is a hot-wall type device, the wafer and the inside wall of the heating furnace are in a state of thermal equilibrium (state in which both temperatures are equal), and the wafer temperature is kept constant regardless of the type or thickness of the film, so the temperature reproducibility is enhanced.

(0015) • Since the heating furnace has a flat shape and can reduce heat dissipation from the openings, the temperature uniformity within the wafer plane is good, even in the case of a small heating furnace. As a result, the handling mechanism for inserting or removing a wafer into or from the inside of the heating furnace can be miniaturized.

(0016) • By switching the flow direction of gas during film formation, the film thickness distribution within the wafer plane that occurs due to changes in concentration along the flow can be reduced. In particular, since the structure of the reaction tube, the gas channel, and the heating furnace is roughly symmetrical with respect to a plane which is positioned in the center of the heating furnace and is orthogonal to the flow of gas (line connecting openings opposite one another so as to sandwich a wafer in the reaction chamber), the film thickness distribution during the first half and the second half is symmetrical, resulting in excellent uniformity in film thickness.

(0017) • Since each edge of the rectangular support plate is larger than the wafer diameter, the film thickness can be prevented from becoming large in the vicinity of the wafer. In addition, since the shape is rectangular, the film thickness distribution within the wafer plane in a direction orthogonal to the flow of gas can be made small.

(0018) • The rectangular support plate is always left inside the heating furnace, and a wafer inserted into the heating furnace is transferred to this support plate and processed, so the wafer increases in temperature rapidly, which causes the temperature to tend to become uniform.

(0019) • Since the structure is such that a wafer is held roughly horizontally and then transferred in the horizontal direction into the heating furnace, handling is simple, and it is easy to accommodate a multiple-chamber system. In addition, in a plasma CVD device or a dry etching device:

- Since gas flows in one direction over the wafer surface, reaction products can be discharged rapidly. Therefore, reaction products never accumulate in the center of the wafer.

(0020) • By performing processing while changing the gas inlets and discharge ports at an intermediate stage so as to change the flow direction of the gas, the same effect as that achieved by rotating the wafer can be achieved more simply, and the uniformization of the film thickness or the etching amount can be achieved.

(0021) • Since it is unnecessary to form holes for circulating the gas in the upper electrode, the electrode structure becomes simple, and abnormal plasma discharge becomes unlikely to occur.

(0022)

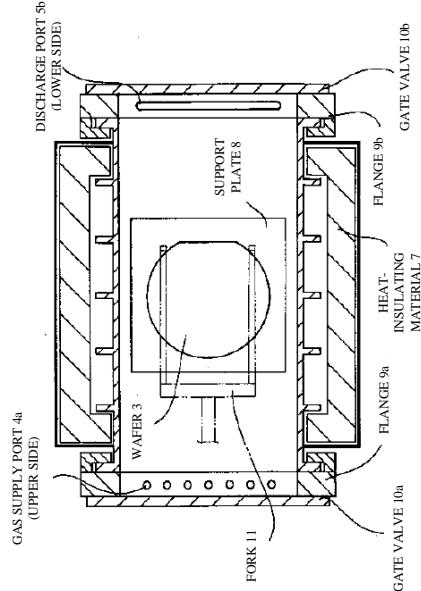

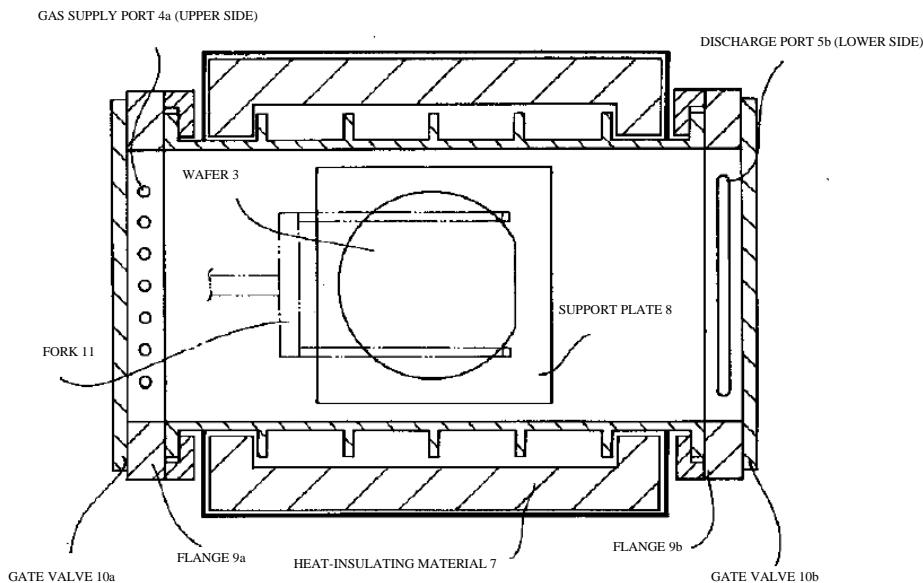

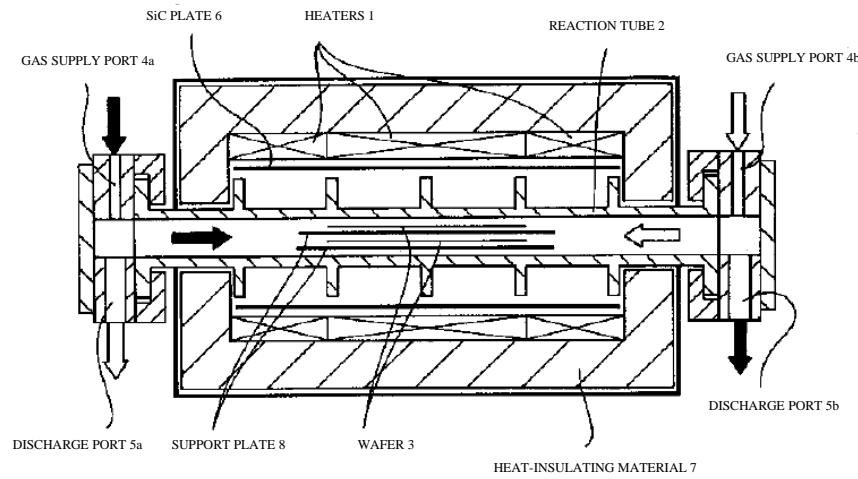

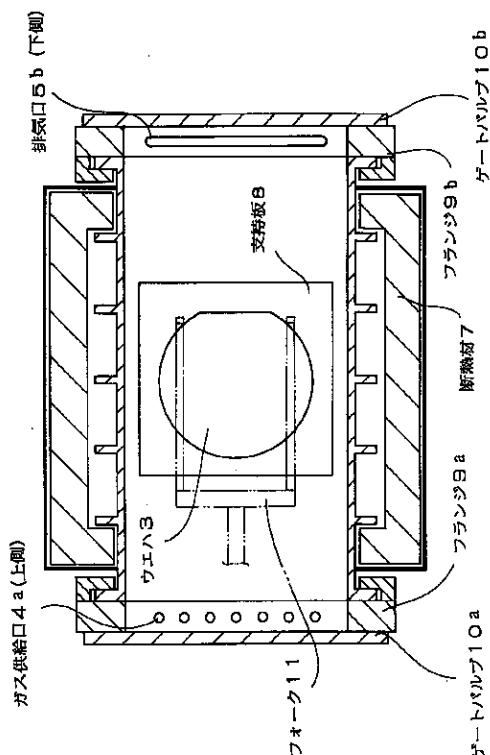

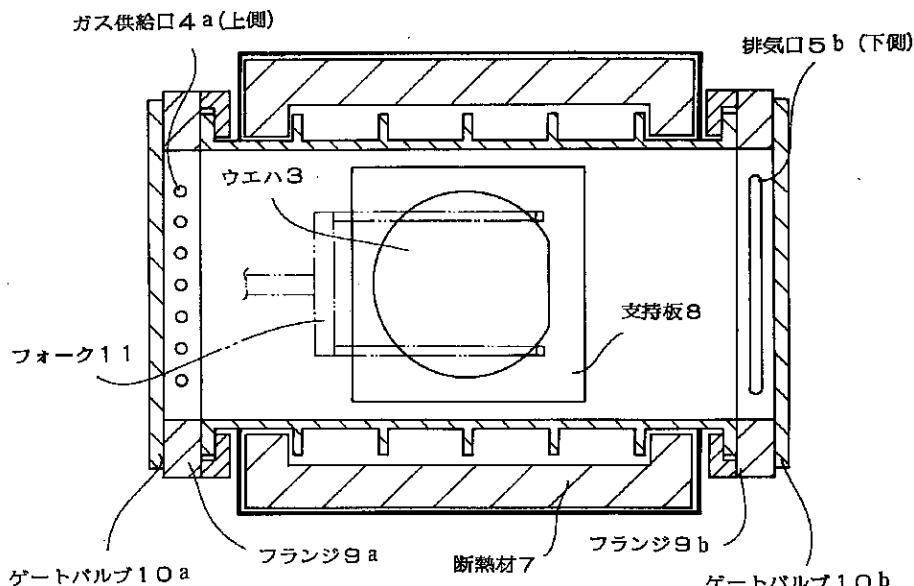

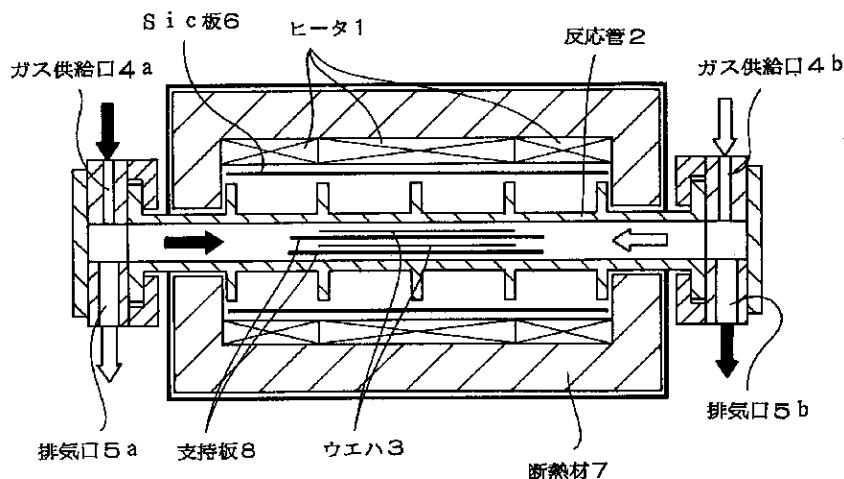

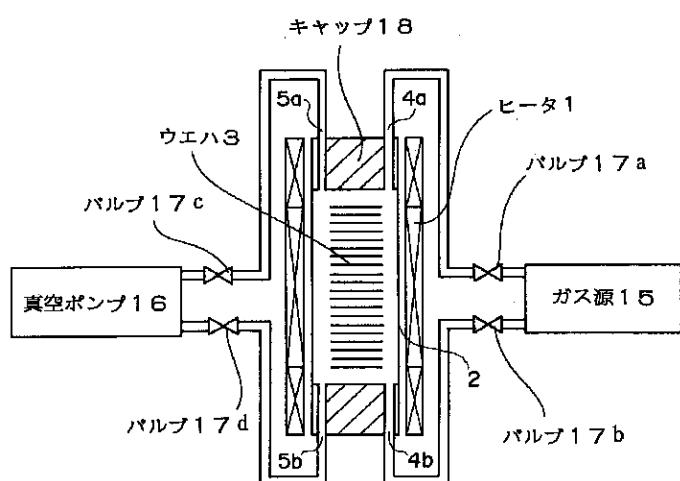

(EXAMPLES) A first example of the present invention will be described hereinafter using the drawings. FIG. 1 is a cross-sectional plan view of a heating furnace of a CVD device to which the present invention is applied when viewed from above, and FIG. 2 is a cross-sectional view of the heating furnace when viewed from the side. The illustrated CVD device includes: a flat reaction tube 2 which is disposed with the axial line roughly horizontal and with both ends opened; a rectangular support plate 8 disposed on two upper and lower layers roughly horizontally inside the reaction tube 2; plate-like heaters 1 disposed opposite one another above and below the reaction tube 2 while sandwiching the reaction tube 2 so as to form a heating furnace; flanges 9a and b coupled to both ends of the reaction tube 2; gas supply ports 4a and b formed within the thickness of the flanges 9a and b in a direction orthogonal to the axial line of the reaction tube 2 and facing upward from the center in the drawing; discharge ports 5a and b similarly formed facing upward from the center of the flanges 9a and b in the drawing; a heat-insulating material 7 provided outside the heater 1; and gate valves 10a and b coupled to the outside of the flanges 9a and b so as to make contact with the central openings of the flanges 9a and b.

(0023) In this device, a wafer 3 is inserted into the reaction tube 2 in a horizontal state and mounted on the support plate 8. The mounted wafer 3 is heated by the heater 1, and a gas is simultaneously supplied from one of the gas supply ports 4a and b while being discharged from one of the discharge ports 5a and b similarly formed at both ends of the reaction tube 2 (on the opposite side as the side to which the gas is supplied so as to sandwich the wafer 3), resulting in the production of a film or epitaxial growth on the surface of the wafer 3. The support plate 8 is provided in two vertical levels so that one

wafer is mounted on each support plate 8, and one or two wafers 3 are processed simultaneously. The gas flows roughly parallel to the surface of the wafer 3. The heater 1 is divided into a plurality of parts, and the amount of heat generated by each part is adjusted so that the temperature distribution of the wafer 3 is uniform. The heat-insulating material 7 is provided on the outside of the heater 1, and consideration is given so as to reduce power consumption by reducing heat dissipation to the surrounding area.

(0024) The gate valves 10a and b are provided on both ends of the reaction tube 2 via the flanges 9a and b, and the wafer 3 is placed on a fork 11 and inserted into the reaction tube 2 through one gate valve 10a in a state in which the gate valve 10a is opened. The inserted wafer 3 is transferred from the fork 11 to the support plate 8, and after the fork 11 is removed, the gate valve 10a is closed so that gas is circulated and a film is formed. Note that the support plate 8 cuts off the operating range of the fork 11.

(0025) When processing two wafers simultaneously as in this example, the support plate 8 is preferably made of transparent quartz. When processing one wafer simultaneously, an opaque hard material such as silicone, SiC, or quartz coated with SiC or polysilicon may be used. At least three feet 8a (not illustrated) are provided on the lower side of the support plate 8 at positions where they do not interfere with the operating range of the fork 11 and at positions as far away from the wafer 3 as possible. When processing two wafers simultaneously, the lower support plate 8 is placed on the inside surface of the lower side wall of the reaction tube 2, and the upper support plate 8 is placed thereon. The upper and lower support plates 8 may be produced as an integrated product. In addition, to make the film thicknesses of the upper and lower wafers equal (assuming that the temperatures are the same), it is crucial to make the distance from the surface of the upper wafer 3 to the inside surface of the upper wall of the reaction tube 2 equal to the distance from the surface of the lower wafer 3 to the lower surface of the upper support plate 8. This is because the growth rate of a film formed on the surface of the wafer 3 depends on the ratio of the area of the surface on which the film is grown and the volume of the space in which the peripheral gas reacts. Therefore, the length of the feet 8a of the support plate 8 is a length that allows this condition to be satisfied.

(0026) In addition, the materials of the support plate 8 and the reaction tube 2 are preferably the same (the materials of the surfaces should be the same). This is because the film forming rate sometimes differs depending on the material, even if the other conditions are the same, and when the film forming rates differ on the support plate 8 and the reaction tube 2, the gas concentration in the gas in the vicinity changes, so the film forming rate changes between the upper and lower wafers as a result.

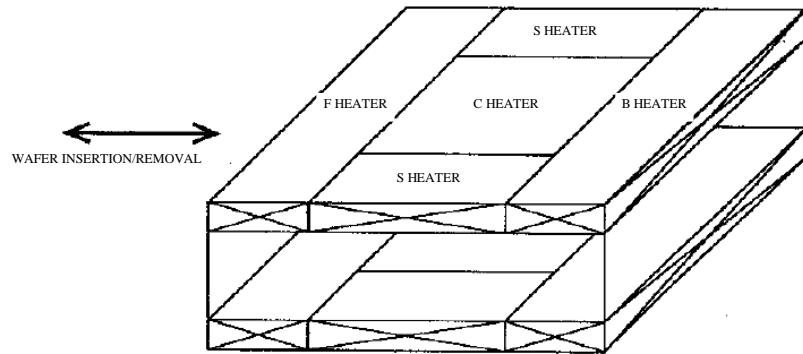

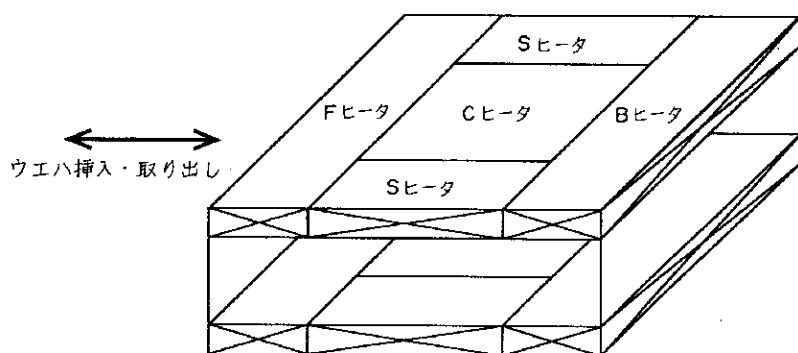

(0027) FIG. 3 illustrates an example of the division of the heater 1. In the illustrated example, the heater 1 consists of a C heater facing the center of the wafer, an F heater on the front side thereof (side where the wafer is inserted), a B heater on the back side, and S heaters on both sides of the C heater. The F and B heaters have a higher heat generation density than the C heater in order to compensate for heat dissipation from the openings provided on both sides of the reaction tube 2. In addition, the S heaters on both sides have a higher heat generation density than the C heater and a lower heat generation density than the F and B heaters. The C heater in the central part is preferably roughly the same size as the wafer.

(0028) FIG. 4 illustrates an example of the shape of the reaction tube. Since the inside of the reaction tube 2 is

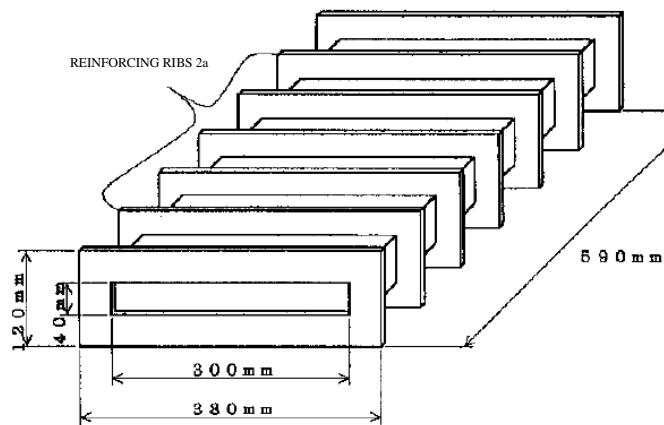

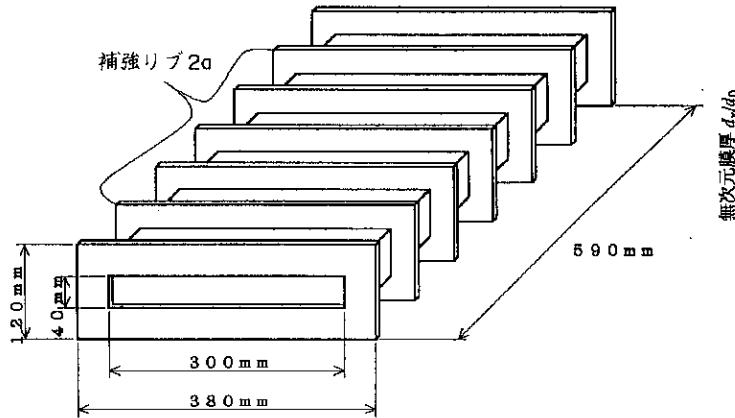

decompressed to not greater than a few Torr during film formation, the reaction tube 2 must be able to withstand an outside pressure of 1 atmosphere. When processing two wafers 3 having a diameter of 200 mm simultaneously with the CVD device of this example, a size of approximately 300 mm wide  $\times$  500 mm deep  $\times$  40 mm high is necessary as the internal dimensions of the reaction tube 2. The reaction tube 2 is often made of quartz, but to withstand an outside pressure of 1 atmosphere at this size, the thickness of the reaction tube 2 must be at least 10 mm. Moreover, at a thickness of 10 mm, tensile stress roughly equivalent to the tensile strength of quartz is generated in the center of the side surface, so the safety factor becomes 1, and the risk of damage in the event of a defect becomes high at the time of production. To achieve strength comparable to that of a batch-type device (since the shape of the reaction tube can be made cylindrical in a batch-type vertical CVD device, strength with a safety factor of around 3 to 5 can be easily achieved with a thickness of around 4 to 6 mm), the thickness of the reaction tube 2 must be not less than 20 mm. However, it is difficult to realize the production of the reaction tube 2 by welding a quartz plate of such a thickness. As illustrated in FIG. 4, the reaction tube 2 of this example is provided with quartz reinforcing ribs 2a in a ring shape at constant intervals on the outside, and these ribs are welded to the main body of the reaction tube. By employing such a structure, the stress generated on the side surface of the reaction tube 2 can be reduced.

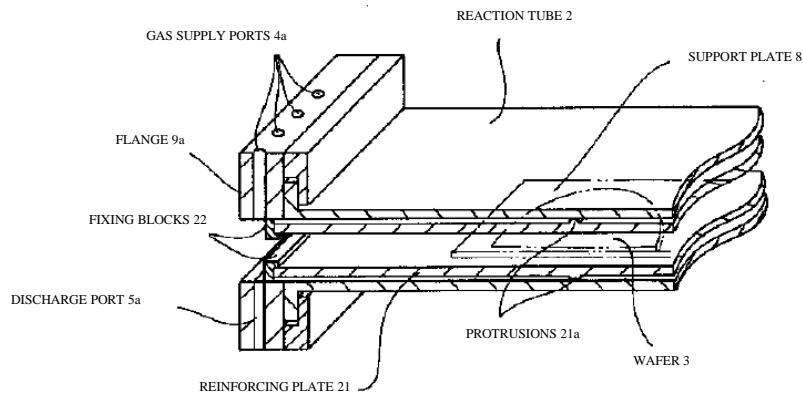

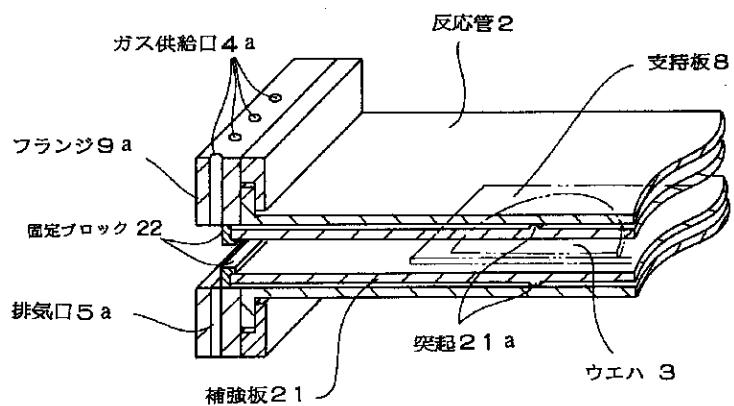

(0029) FIG. 5 illustrates another example in which a quartz reinforcing plate 21 is inserted into the reaction tube 2. The reinforcing plate 21 may also be made of a heat-resistant material such as SiC or Si rather than quartz. The reinforcing plate 21 is formed into a plate shape, both ends of which are fixed to the flanges 9a and b by fixed blocks 22. Protrusions 21a provided on the surfaces of the reinforcing plate 21 oppose the inside surface of the reaction tube, and the plate is kept parallel to the inside surfaces of the reaction tube so that the protrusions make contact with the central part of the inside surfaces of the reaction tube 2. The thickness of the reinforcing plate 21 is selected appropriately in accordance with the material that is used. Bending occurring in the reaction tube 2 due to outside pressure is greatest in the central part, so supporting this part with the reinforcing plate 21 makes it possible to reduce stress occurring on the side surface of the reaction tube 2.

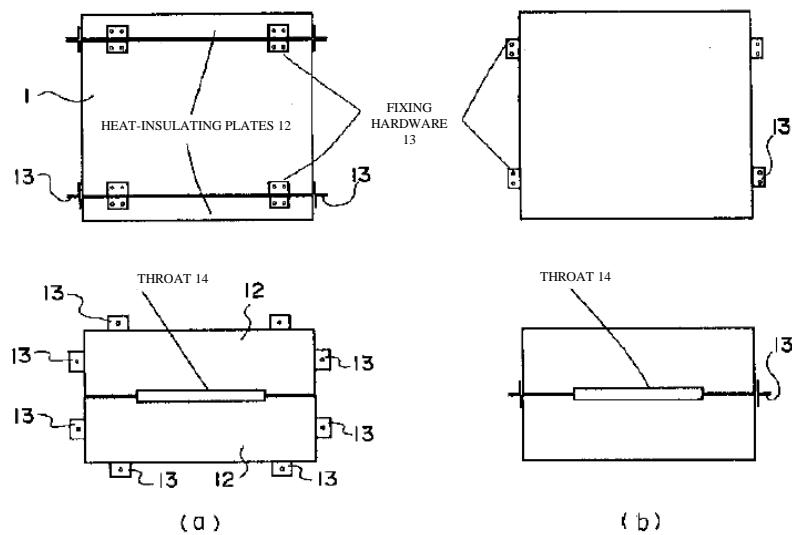

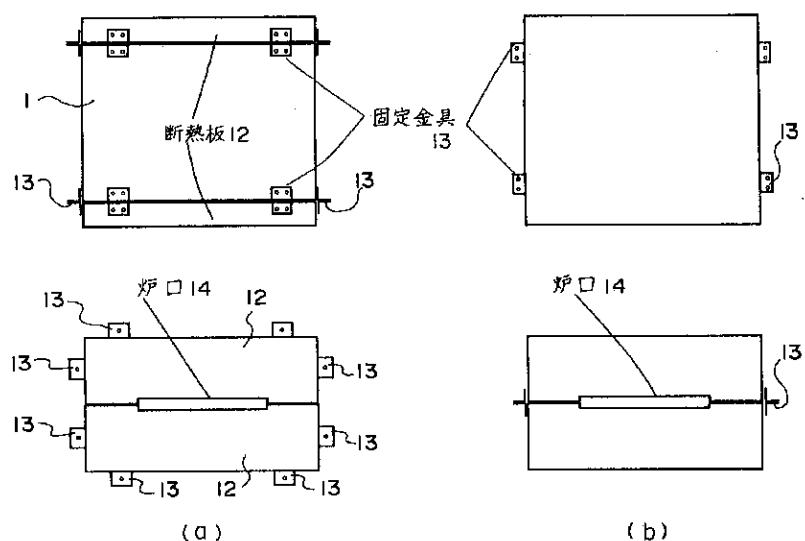

(0030) The reason for giving the heating furnace flat, which is a main point of the present invention, is to reduce heat dissipation by making the opening small so as to be able to make the temperatures of the wafers 3 uniform, even with a small heating furnace. Here, in the CVD device illustrated in FIGS. 1 and 2, the flat shape is preferable such that the height of the opening is low enough that the ratio of the furnace inside length (length from the inside of the heat-insulating material to the inside with respect to the wafer insertion direction) and the height of the opening is at least greater than 5. Next, a heating furnace structure for making the height of the opening low will be described. FIG. 6 is an outline drawing illustrating the structure of the heating furnace of the present invention. In the case of an integrated heating furnace, an opening of a size that at least allows the reinforcing ribs to pass through is required to insert the reaction tube 2 illustrated in FIGS. 4 and 5 into the furnace. However, by dividing the heating furnace into a plurality of parts as illustrated in FIG. 6, the opening can be made smaller than the reinforcing ribs. The example illustrated in FIG. 6(a) consists of a heating furnace main body made of a

heater 1 and heat-insulating plates 12 attached to both ends in the axial direction thereof, and the heat-insulating plates 12 are divided into two parts vertically. The reaction tube 2 is inserted into the furnace in a state in which the heat-insulating plates 12 are removed, and the heat-insulating plates 12 are subsequently attached to the heating furnace main body 1 by fixing hardware 13. The gap (throat 14) between the upper and lower heat-insulating plates 12 is of a size that allows the reaction tube 2 main body – excluding the reinforcing rib 2a – to pass through. The heat-insulating plates 12 are detachably attached to the heating furnace main body by the fixing hardware 13. FIG. 6(b) is an example in which the heating furnace main body is divided into two parts vertically, and after the reaction tube 2 is mounted to the lower heater by removing the upper heater, the upper heater is overlaid from above to form a heating furnace.

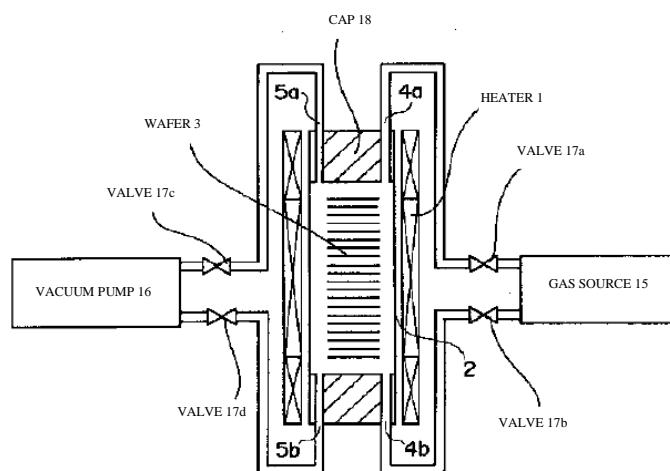

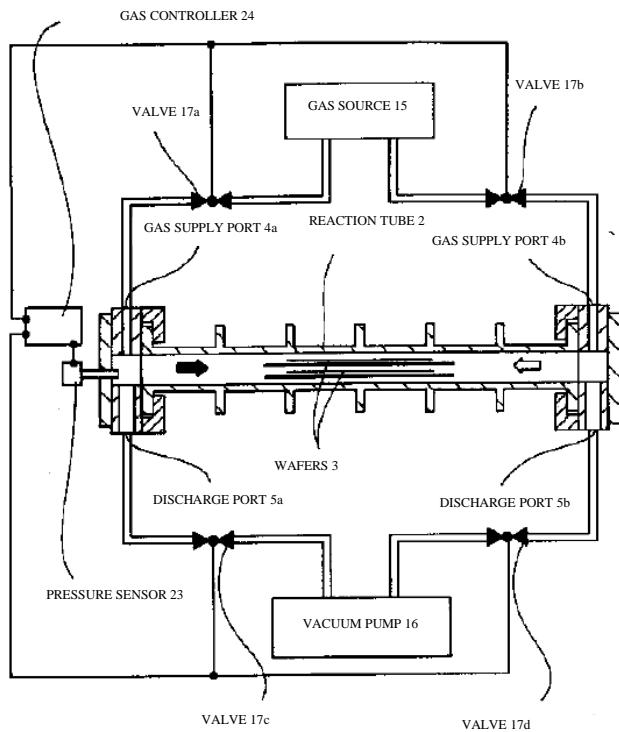

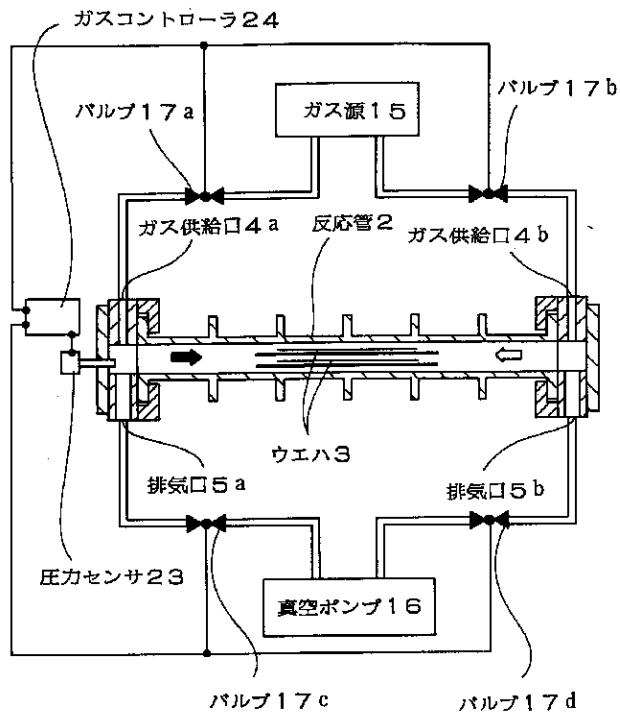

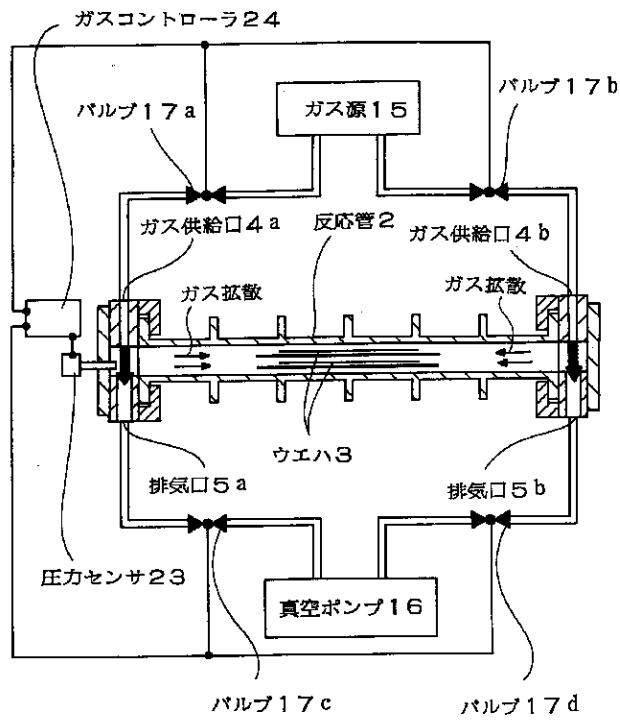

(0031) FIG. 7 is a system diagram of the gas supply system and the discharge system of the example illustrated in FIG. 1. Flanges 9a and b are provided on both sides in the axial direction of the reaction tube 2, and the gas supply port 4a and the discharge port 5a are attached to the flange 9a, while the gas supply port 4b and the discharge port 5b are attached to the flange 9b. The gas supply ports 4a are connected to a gas supply 15 through valves 17a and b, and the discharge ports 5a and b are connected to a vacuum pump 16 through valves 17c and d. A wafer 3 is inserted into the reaction tube 2 and heated, and after the wafer 3 reaches a prescribed temperature, a gas is circulated for a prescribed amount of time to form a film.

(0032) In the first half of film formation, the valves 17a and 17d are opened and the valves 17b and 17c are closed so that gas is supplied. At this time, the reaction gas flows from left to right inside the reaction tube 2, as indicated by the black arrow in the drawing. Once the first half of film formation is complete, the valves 17a and 17d are closed and the valves 17b and 17c are opened. At this time, the gas flows from right to left inside the reaction tube 2, as indicated by the white arrow in the drawing.

(0033) From the perspective of shortening the film forming time, it is preferable to switch the open/closed states of the valves 17a, b, c, and d in a short amount of time, but there are some cases in which problems arise wherein the pressure inside the reaction tube 2 and the flow of gas change rapidly so that reaction products adhering to the vicinity of the openings of the reaction tube 2 peel off. In this case, the gas is switched in accordance with the following procedure.

(0034) (1) The discharge port 5a is gradually closed, and the discharge port 5b is gradually opened.

(0035) (2) Once the discharge port 5a closes completely and the discharge port 5b opens completely, the gas supply port 4a is gradually opened and the gas supply port 4b is gradually closed.

(0036) (3) During this time, the pressure inside the reaction tube 2 is measured with a pressure sensor 23, and a gas controller 24 adjusts degrees of opening of the valves 17a, b, c, and d so that the pressure inside the reaction tube 2 is constant.

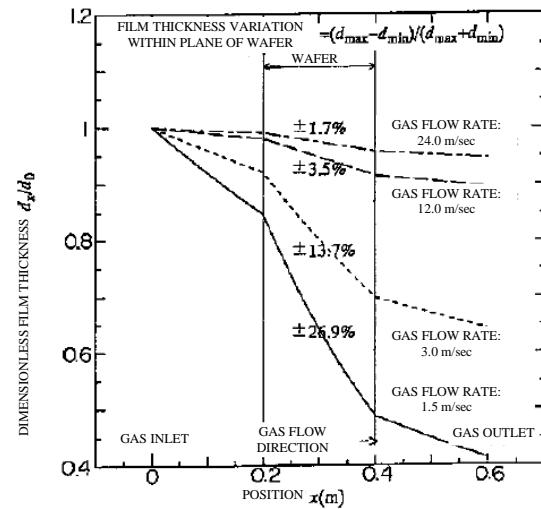

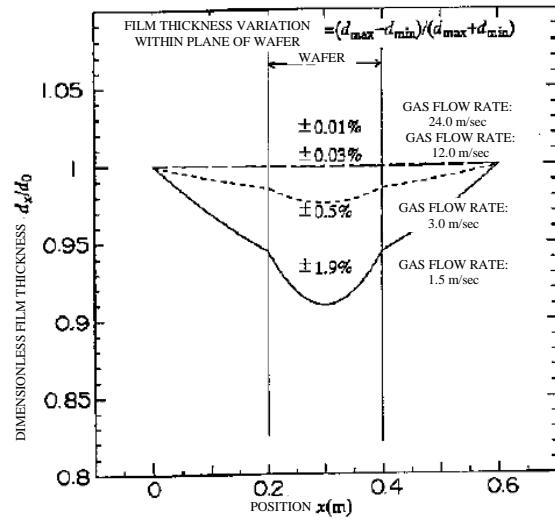

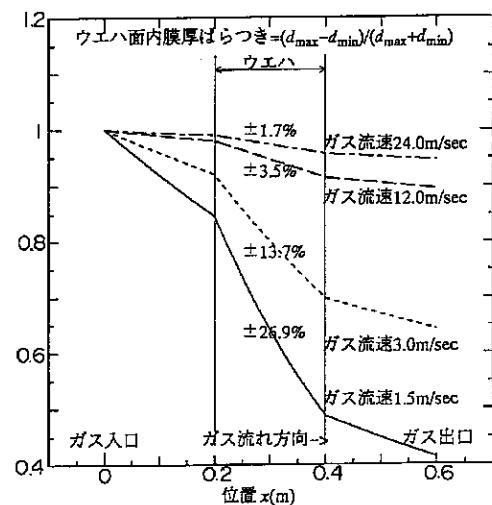

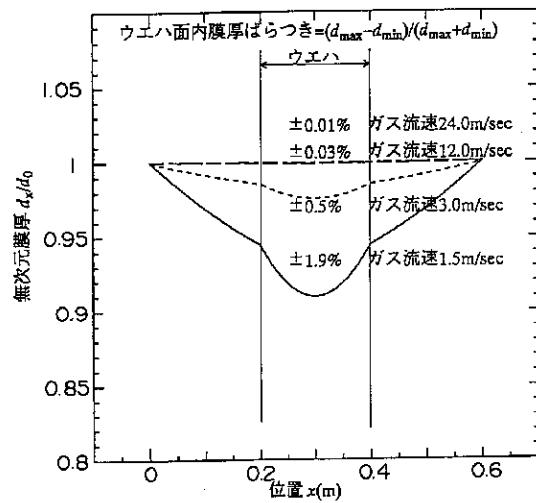

(0037) The film forming rate distribution of a film formed on a wafer when the flow direction of the gas inside the reaction tube is not switched is illustrated in FIG. 8. This shows the results of calculating the film forming rate distribution when an  $\text{Si}_3\text{N}_4$  film is attached using  $\text{NH}_3$  and  $\text{SiH}_2\text{Cl}_2$ . Symbol  $dx$  indicates the film thickness of a position at a distance  $x$  from the gas inlet in the gas flow direction, and symbol  $do$  indicates the film thickness at the gas inlet. By increasing the gas flow rate (increasing the flow volume) and reducing the proportion of the supplied gas that is consumed in the reaction, a roughly uniform film thickness

distribution is obtained, as indicated by the dotted-dashed line, for example, but problems arise such as: (1) a large amount of gas is consumed; and

(0038) (2) the wafer is cooled by the gas so that the in-plane temperature uniformity is lost.

(0039) [text translated at the end of paragraph 0037]

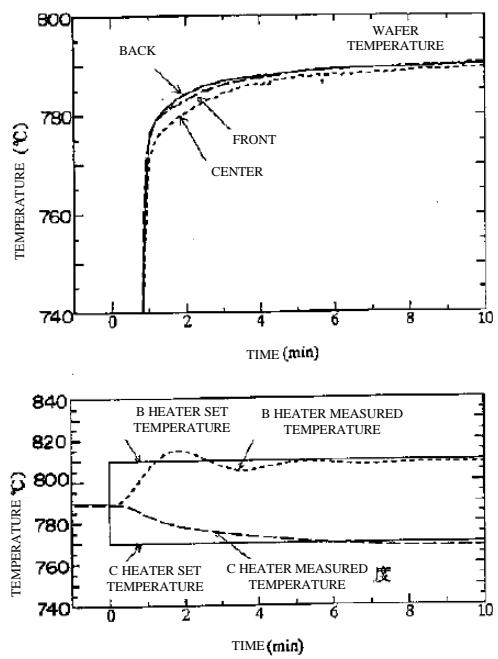

(0040) The results of the same calculations when the gas flow is switched at an intermediate stage are shown in FIG. 9. It can be seen from the drawing that as a result of the superimposition of the film forming rate distributions of the first and second halves of film formation, a film with a uniform thickness is obtained at a lower gas flow volume (flow rate: 12.0 m/sec). Here, a point particularly crucial to making the film thickness distribution uniform is to make the film forming rate distributions of the first and second halves symmetrical with respect to the center position. Here, it is important to make the structure of the device symmetrical and to make the gas flow, concentration, temperature distribution, and the like symmetrical with respect to the central position of the wafer in the axial direction of the reaction tube. In the sheet-type CVD device illustrated in this example, the structures of the heater 1 and the reaction tube 2 are completely symmetrical with respect to the central position in the axial direction of the reaction tube, so the uniformity of the film thickness is even better than in conventional cases.

(0041) The gas switching period is such that the gas flow would be switched between the first and second halves of film formation if the temperature of the wafer 3 were to reach a steady state. However, when the temperature of the wafer 3 also changes during film formation, as described below, the flow must be switched with a shorter period.

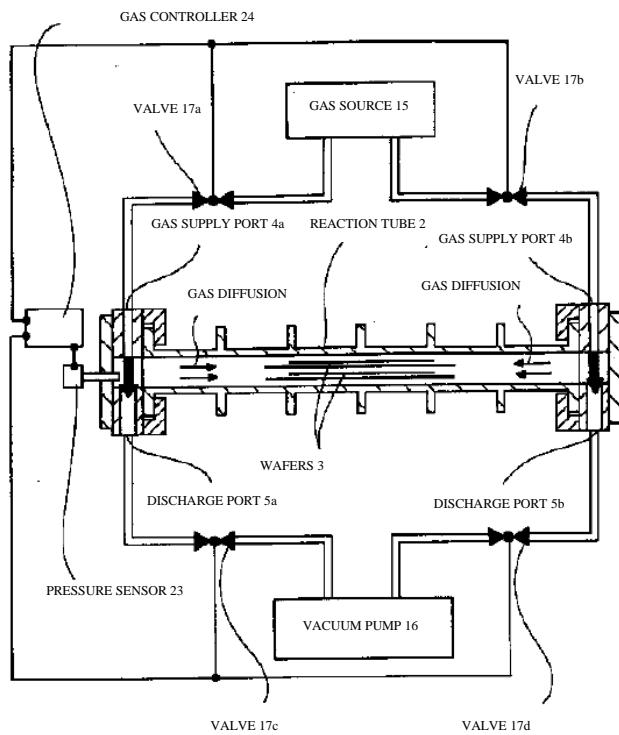

(0042) FIG. 10 illustrates a second example of the present invention, which is an example of a vertical CVD device having two openings, wherein the structures of the heating furnace and the reaction tube 2 are vertically symmetrical. In the example illustrated in FIG. 10, an opening is also provided on the upper side of the reaction tube 2 in the same manner as on the lower side, and caps 18 are attached to the upper and lower openings. Wafers 3 are inserted from below in the same manner as in a conventional device, and a cap 18 similar to that on the upper side is attached to the bottom thereof. The heater is divided into four zones, for example, including two zones in the central part and two zones at the edges so that the temperature distribution of the wafers is vertically symmetrical. In addition, when the gas is made to flow from bottom to top during the first half, the gas is made to flow from top to bottom during the second half. Since the structure is vertically symmetrical, the flow is completely vertically symmetrical with the exception of the effects of gravity (the effects of gravity are small since the process is a low-pressure process). As a result, as in the case of the sheet-type CVD device of the first example illustrated above, the film thickness uniformity among wafers is enhanced.

(0043) Note that in the two examples described above, cases in which two openings are formed in the reaction tube 2 were described, but there may be three or more openings, and the gas supply ports and discharge ports may be changed at suitable times to change the gas flow direction to three or more directions. For example, a step of providing a gas supply port 4c in the center, supplying a gas from the gas supply port 4c, and discharging the gas from the discharge ports 5a and 5b at both ends may be added to the two steps described above. As a result, it is possible to correct decreases in film thickness in the center of the wafers 3 and to make the film thickness distribution uniform.

(0044) In addition, when the diffusion of the gas is fast, in a

sheet-type CVD device, as illustrated in FIG. 11, all of the valves 17a, b, c, and d may be opened so that the gas introduced from the gas supply ports 4a and 4b is quickly discharged from the discharge ports 5a and 5b, and the gas may be supplied to the wafers 3 by diffusion alone so that the film thickness within the plane of the wafers 3 is uniform.

(0045) Further, in this example, as illustrated in FIG. 1, the support plate 8 is rectangular, so the gas flow and the gas concentration distribution along the flow are roughly the same in the center and at the ends of the wafer (at the upper side or lower side in FIG. 1). Therefore, the film thickness distribution within the plane of the wafer becomes small in a cross-section orthogonal to the flow. In addition, as illustrated above, when processing two wafers 3 simultaneously, the spacing between the upper surface of the upper wafer 3 and the inside surface of the upper wall of the reaction tube 2 and the spacing between the upper surface of the lower wafer 3 and the lower surface of the upper support plate 8 must be equal. As a result, the gas flow and gas concentration are roughly the same for the upper and lower wafers 3, and the difference in film thickness between the two wafers can be made small.

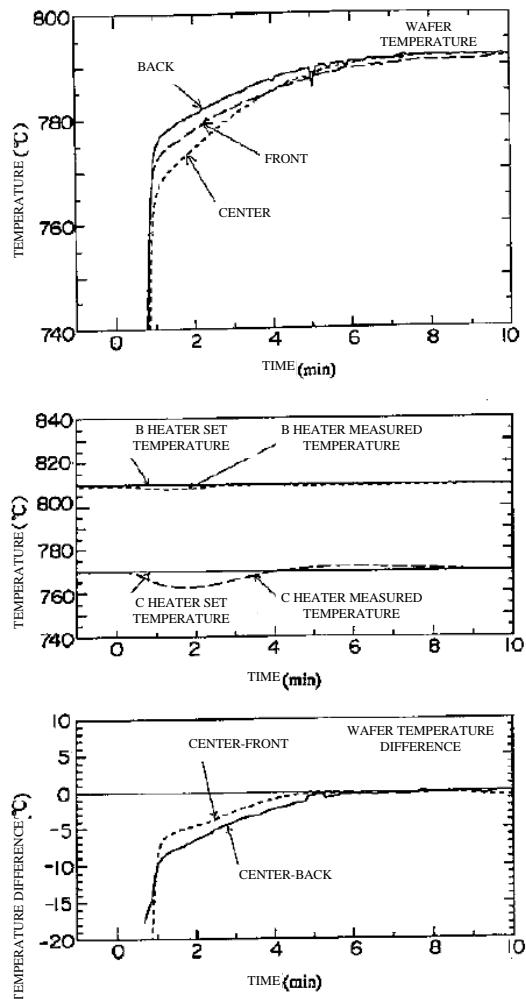

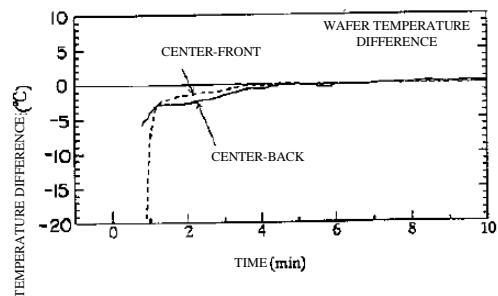

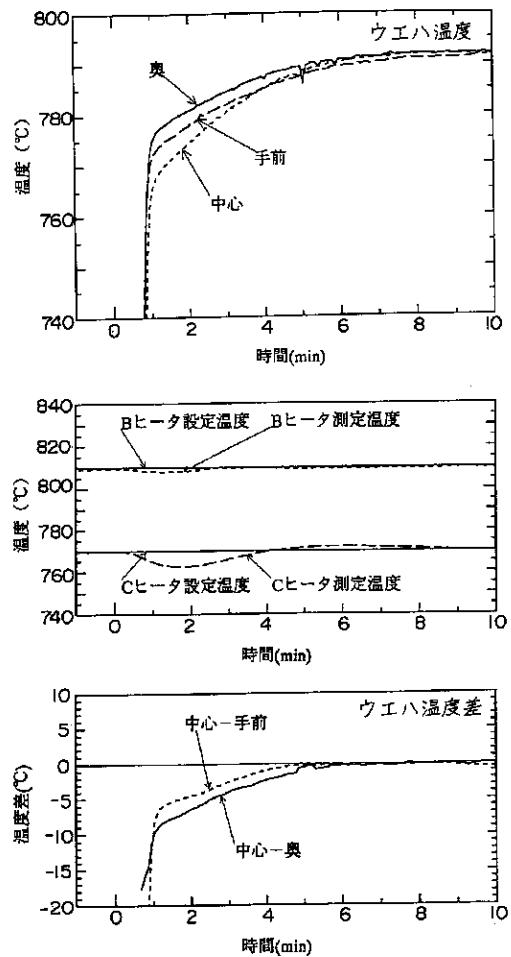

(0046) Next, a method of reducing the temperature distribution within the plane of the wafer will be described. Changes over time in the temperature of the wafer when the wafer 3 is inserted into the sheet-type CVD device illustrated in FIG. 1 ((a) in the drawing), the heater temperature ((b) in the drawing), and temperature differences based on the center of the wafer are shown in FIG. 12 (a wafer 200 mm in diameter was inserted into the furnace, and the heater set temperature was adjusted so that the wafer temperature deviation was within a range of  $\pm 1^{\circ}\text{C}$  with respect to a prescribed temperature at a point when a steady state was reached). The temperature of the wafer 3 increases rapidly immediately after the wafer is inserted into the heating furnace and reaches a roughly steady temperature in approximately one minute, after which the temperature gradually increases and approaches the furnace internal temperature. The temperature of the heater temporarily drops due to the insertion of the cold wafer 3 and then returns to the original temperature after a few minutes have passed. Here, the temperature drop of the C heater directly facing the wafer 3 is largest. These factors cause the temperature increase of the wafer 3 to be fastest in order of the back and the sides, followed by the front and the center.

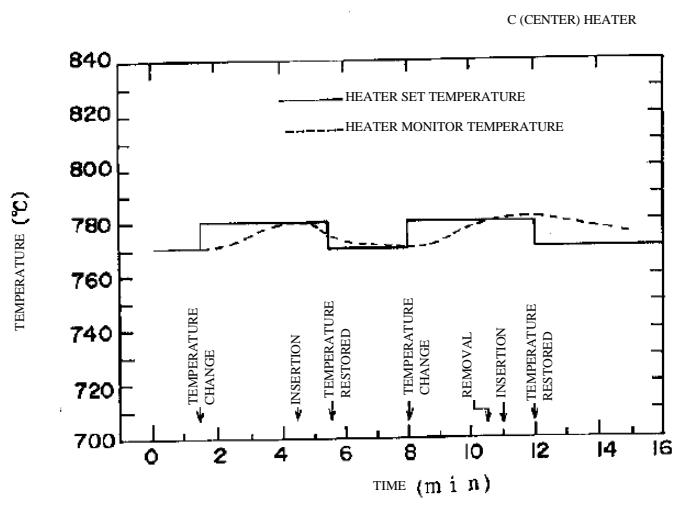

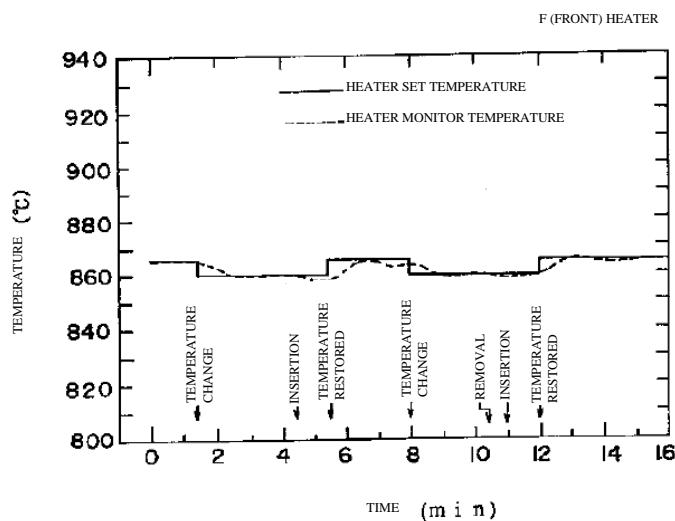

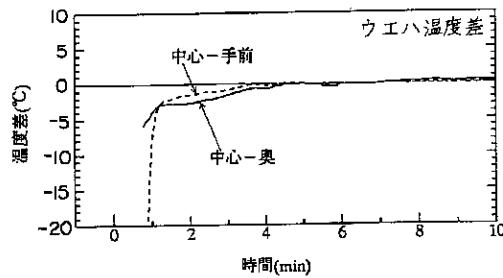

(0047) To reduce the temperature distribution of the wafer 3, it is effective to hasten the temperature increase in the center. Therefore, the set temperature of the C heater may be set to a high level or the set temperatures of the B and S heaters may be set to a low level until the point when the wafer 3 is inserted, for example. Changes in the temperature of the wafer 3 when such temperature control is administered are illustrated in FIG. 13. The temperature increase in the center of the wafer becomes fast, and the temperature distribution within the plane of the wafer becomes small at the point when film formation is begun.

(0048) Here, an example in which the set temperature of each heater is switched at the point when the wafer 3 is inserted was described, but switching may occur at other points in time, and the heater set temperature may also be changed a plurality of times during one cycle of processing.

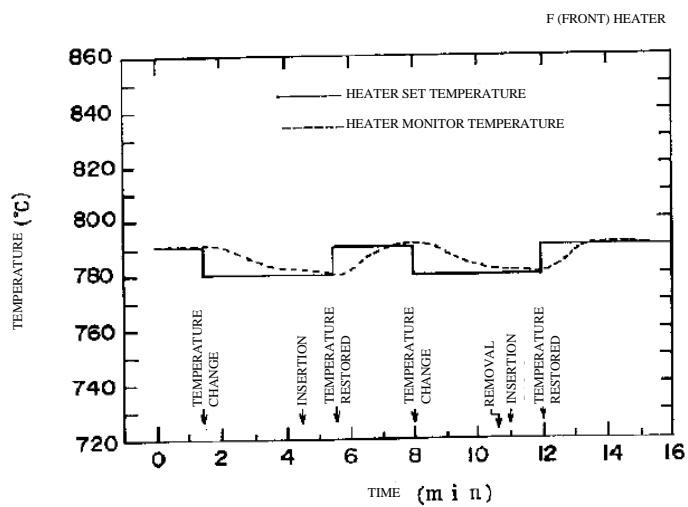

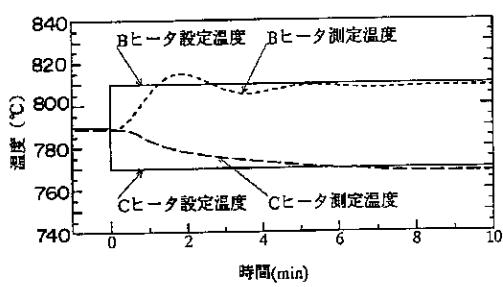

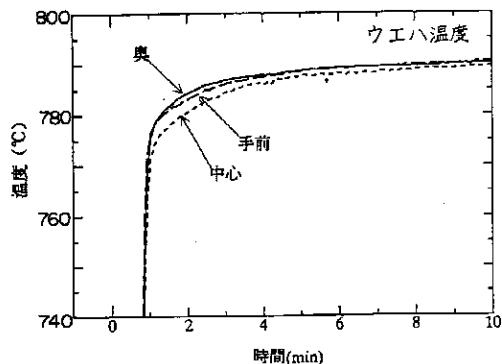

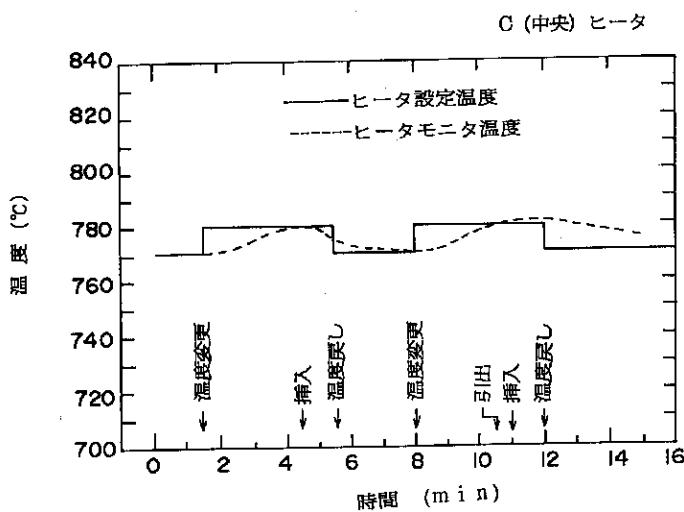

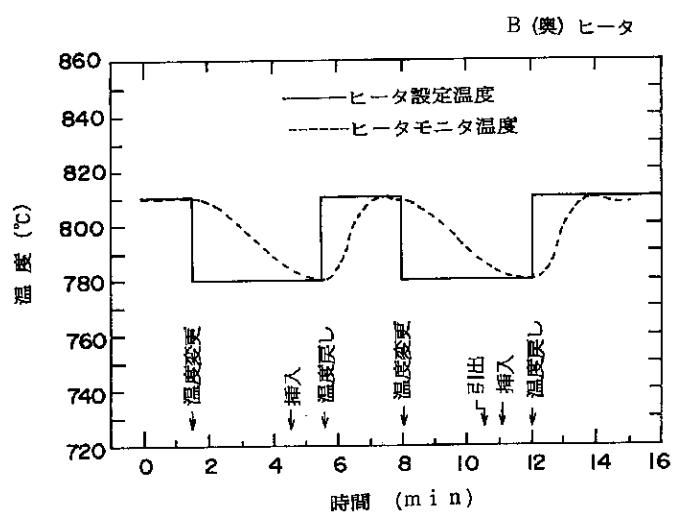

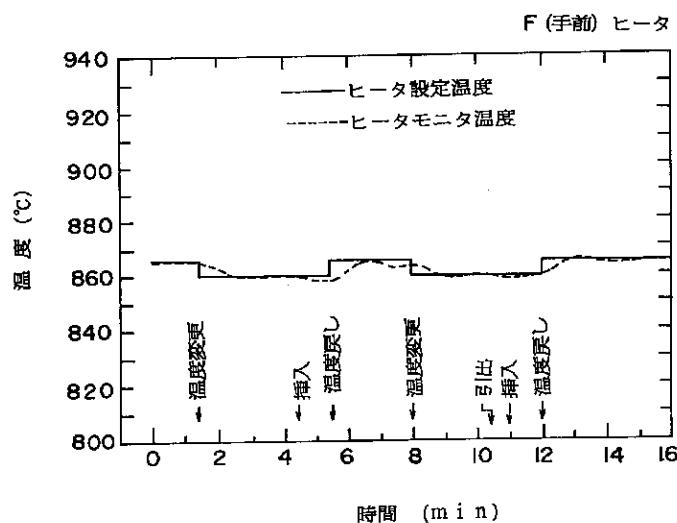

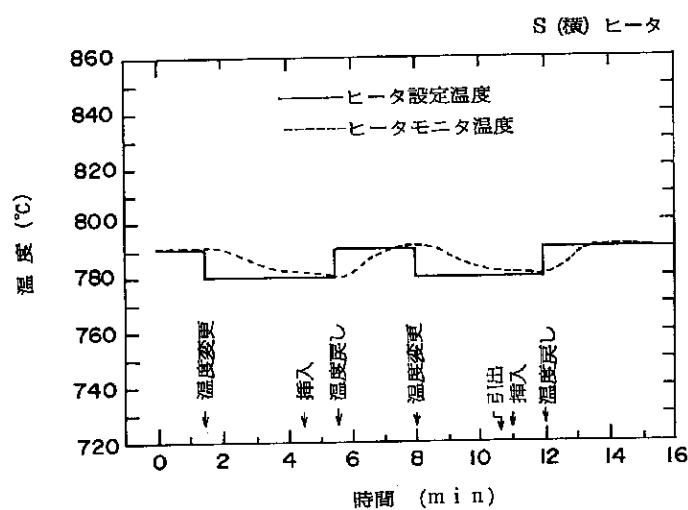

(0049) An example of this is illustrated in FIGS. 14 to 17 (one cycle=6 min, 30 sec).

(0050) This consists of the following procedure:

(1) The set temperature is changed before the first wafer is inserted (the temperatures of the peripheral heaters B, F, and S are lowered, and the temperature of the central heater C is increased).

(2) Once a certain amount of time has passed after the wafer is inserted, the set temperature is returned to the original temperature.

(0051) (3) A certain amount of time prior to the removal of the wafer (before the second wafer is inserted), the set temperature is changed in the same manner as before the first wafer is inserted.

(0052) (4) The procedure from (1) to (2) above is repeated.

(0053) (Hereinafter, when the heater set temperature is changed based on this procedure, the period during which the respective set temperature is constant will be called an "event"). The changing pattern of the set temperature of each heater is determined in advance (feed forward control).

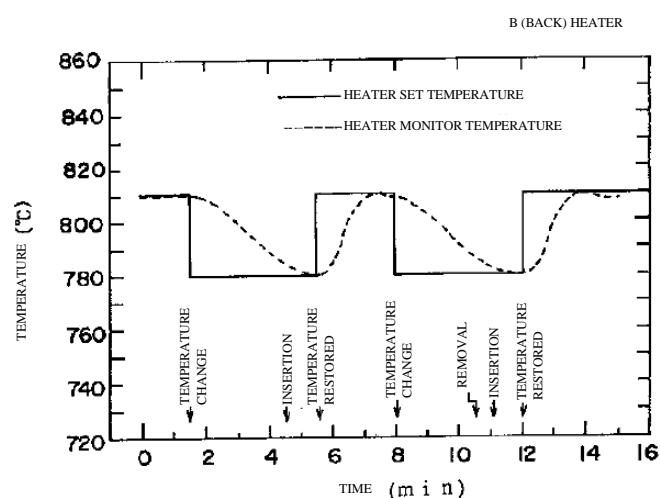

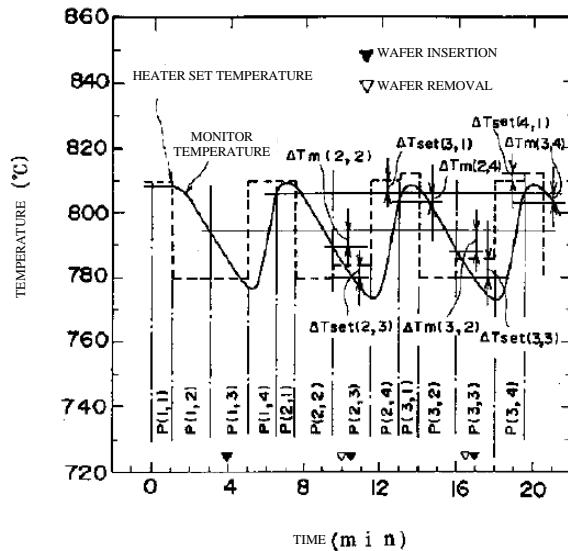

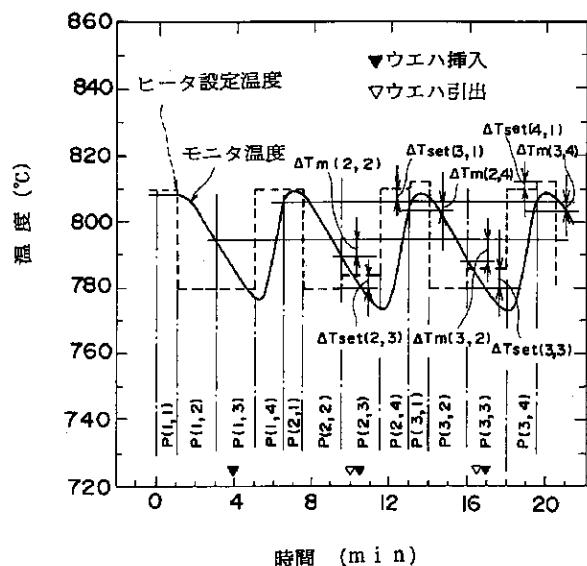

(0054) In addition, it can be seen from FIG. 12 that after a wafer is inserted, it takes 5 to 6 minutes for the heater temperature to recover to a steady state. When processing is repeated for a smaller amount of time, the furnace internal temperature gradually changes (decreases in many cases) in the second and subsequent cycles of processing. Therefore, it is necessary to correct the decreases in processing temperature by gradually increasing the set temperature of the heater by means of the number of cycles of processing. An example of this method is illustrated in FIG. 18. Here,  $P(i, j)$  refers to the  $i^{\text{th}}$  process and the  $j^{\text{th}}$  event with respect to the wafer.

(0055) The method of determining the set temperature is as follows:

(1) The difference  $\Delta T_m(n, j-1)$  between the heater temperature  $T_m(n, j-1)$  at the end of process  $n$  and event  $j-1$  and the heater temperature  $T_m(1, j-1)$  at the same time as the first process performed on the wafer is determined.

(0056) (2) A correction value  $\Delta T_{\text{set}}(n, j)$  ( $\Delta T_{\text{set}}(n+1, 1)$  in the final event) is determined with the following formula from the temperature difference  $\Delta T_m(n, j-1)$  using appropriate coefficients  $a(j)$  and  $b(j)$ , and the set temperature  $T_{\text{set}}(n, j)$  ( $T_{\text{set}}(n+1, 1)$  in the final event) of the next event  $P(n, j)$  ( $P(n+1, 1)$  in the final event) is then determined.

(0057) This is expressed by the following formula:

$$T_{\text{set}}(n, j) = T_{\text{set}}(1, j) + \Delta T_{\text{set}}(n, j) = T_{\text{set}}(1, j) + a(j) \times \Delta T_m(n, j-1) + b(j).$$

(0058) FIG. 18 is an example in which the control described above was administered on the B (back) heater at the end of the second and fourth events, and the same control may also be administered for the other heaters.

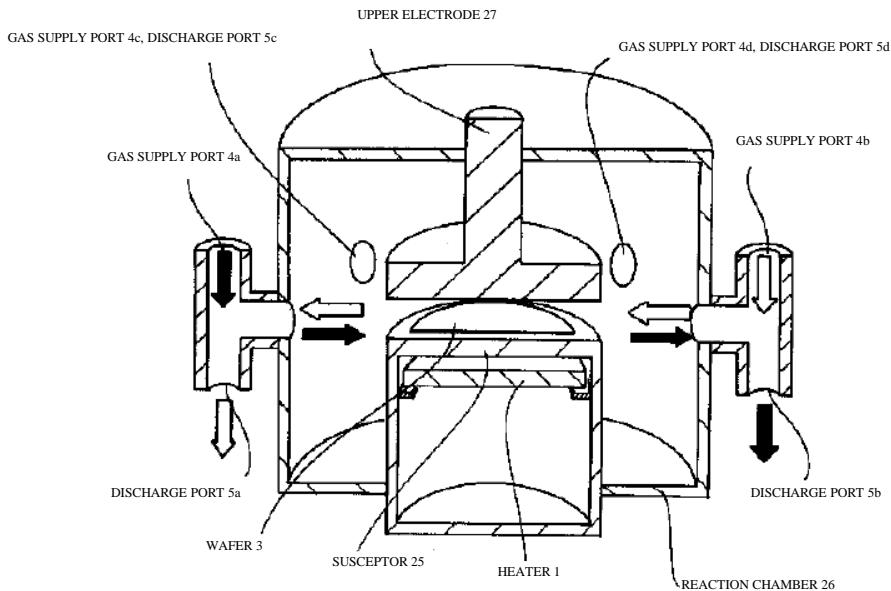

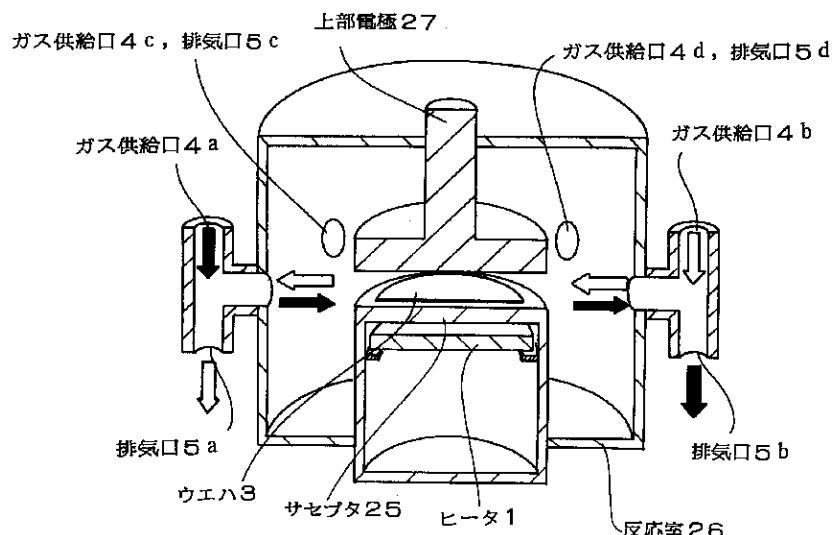

(0059) Next, an example in which the gas supply method of the present invention is applied to a device other than a thermal CVD device will be described. FIG. 19 illustrates a cross-section of a plasma CVD device according to the present invention. The illustrated device includes: a reaction chamber 26 which forms a cylindrical shape with both ends closed and is disposed with the axial line positioned vertically; a susceptor 26 [sic: 25] built into the reaction chamber 26 with a horizontal wafer mounting surface; an upper electrode 27 disposed opposite an electrode surface on the wafer mounting surface of the susceptor 26 [sic: 25]; a plurality of openings formed in a wall surface portion of the reaction chamber 26 sandwiched by lines at which the extended plane of the electrode surface of the upper electrode 27 and the extended plane of the wafer mounting surface of the susceptor 26 [sic: 25] intersect with the wall surface of the reaction chamber 26;

and gas supply ports 4a, b, c, d, ... and discharge ports 5a, b, c, d, ... respectively connected to the plurality of openings. A heater 1 is disposed beneath the wafer mounting surface of the susceptor 26 [sic: 25].

(0060) In a device with the configuration described above, a wafer 3 is placed on (the wafer mounting surface of) the susceptor 25 with a built-in heater 1 and is heated by the heater 1. A gas is supplied from the gas supply port 4a provided in the side wall of the reaction chamber 26, and the gas is discharged from the discharge port 5b. A high-frequency voltage is supplied between the upper electrode 27 and the wafer 3 to generate plasma, and the gas is decomposed to form a film on the surface of the wafer 3. During film formation, the flow of gas is switched so that the gas is supplied from the gas supply port 4b and discharged from the discharge port 5a. As a result, reaction products generated in response to the reaction due to the flow of gas over the wafer 3 can be discharged rapidly, and the film thickness distribution within the plane of the wafer 3 can be made small. Further, a step of supplying a gas from the gas supply port 4c and discharging the gas from the discharge port 5f (not illustrated) positioned on the front right side, a step of supplying a gas from the gas supply port 4d and discharging the gas from the discharge port 5e (not illustrated) positioned on the front left side, and a step of circulating the gas in the respective opposite directions may be added, and the number of gas supply ports and the number of discharge ports are not particularly limited. Note that for a process in which a hot-wall type CVD device cannot be used for some reason, using a thermal CVD device in which the upper electrode 27 is removed from the plasma CVD device illustrated in FIG. 10 is effective for the uniformization of the film thickness.

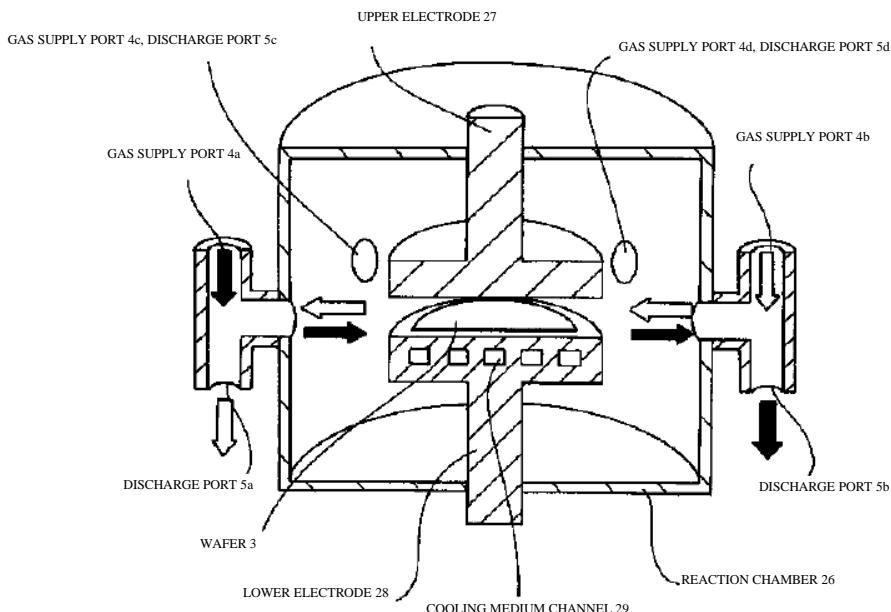

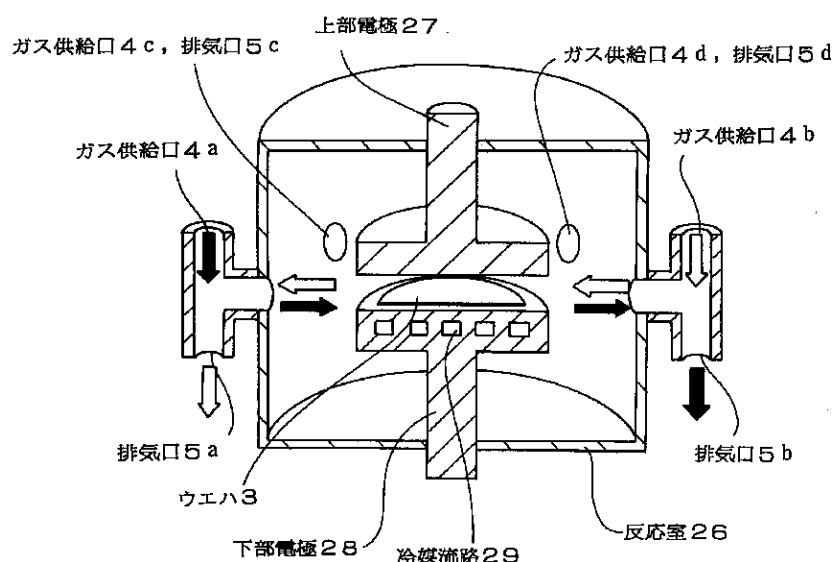

(0061) FIG. 20 is a drawing illustrating a cross-section of a parallel plate type plasma etching device according to the present invention. The illustrated device is provided with a lower electrode 28, the upper surface of which is an electrode surface also functioning as a wafer mounting surface, instead of the susceptor 26 [sic: 25] of the device illustrated in FIG. 19, so a cooling medium channel 29 is formed inside the lower electrode below the wafer mounting surface. The configuration is otherwise the same as that of the device illustrated in FIG. 19, so the same symbols are used, and explanations thereof will be omitted. In a device having the configuration described above, a wafer 3 is placed on the wafer mounting surface (electrode surface) of the lower electrode 28, and an etching gas is supplied from the gas supply port 4a provided in the side wall of the reaction chamber 26 and discharged from the discharge port 5b. High-frequency waves are supplied between the upper electrode 27 and the wafer 3 to generate plasma, and the etching gas is decomposed to etch a film formed on the surface of the wafer 3. A cooling medium is circulated to the cooling medium channel 29 provided in the lower electrode 28, and the wafer 3 is cooled to a prescribed temperature. The flow of gas is switched during etching so that the etching (gas) is supplied from the gas supply port 4b and discharged from the discharge port 5a. As a result, reaction products can be discharged rapidly, as in the case of a plasma CVD device, and the distribution of the etching rate within the plane of the wafer 3 also becomes small. Further, as described in the example of the plasma CVD device, a step of circulating a gas from a different direction may also be added.

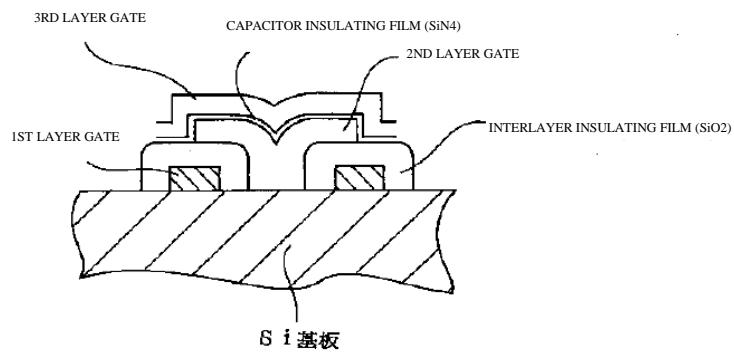

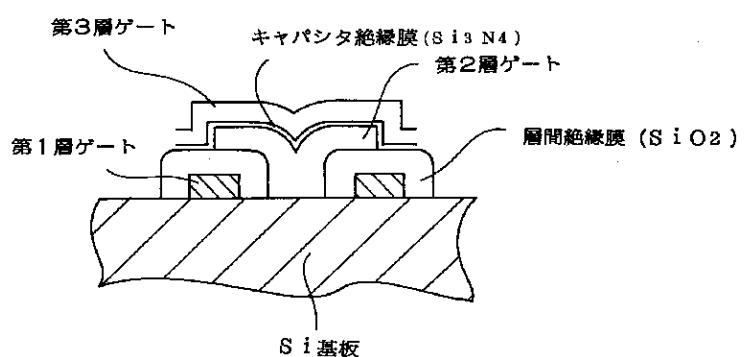

(0062) FIG. 21 is a schematic diagram of a DRAM cell with an STC (Stacked Capacitor) structure. Examples of films formed using the thermal CVD device of the present invention in the

production process of such a DRAM include a polysilicon film or a phosphorus-doped polysilicon film used for gate electrode wiring, a phosphorus glass film used as an interlayer insulating film, and an  $\text{Si}_3\text{N}_4$  film used as a capacitor insulating film. Of these, the step in which the uniformization of the film thickness has recently become particularly important is the capacitor forming step, and suppressing the thinning of an  $\text{Si}_3\text{N}_4$  insulating film and the formation of a natural oxide film has become a critical issue. The effectiveness of using the film forming device or etching device according to the present invention for such a capacitor forming step will be described hereinafter. The basic performance of the sheet-type thermal CVD device according to the present invention is such that unevenness in film thickness due to variation in temperature or gas concentration between wafers is smaller than in conventional devices, so the storage capacity of the capacitor can be increased by further reducing the thickness of the capacitor film. Further, configuring a multiple-chamber device (device in which a plurality of processing devices are connected to a central chamber, and a wafer is inserted into each processing device by a handling robot disposed therein so as to continuously perform processing such as film formation or etching; the wafer can be processed continuously without being exposed to the atmosphere) by combining the CVD device and the etching device according to the present invention and forming a capacitor without bringing the wafer into contact with the atmosphere through the procedure of (1) forming a polysilicon film for a second layer gate electrode wiring with the thermal CVD device, (2) etching the second layer gate electrode wiring into a prescribed pattern with the etching device, (3) forming an  $\text{Si}_3\text{N}_4$  capacitor insulating film thereon with the thermal CVD device, and (4) forming a polysilicon film for a third layer gate electrode wiring in the next reaction chamber is effective for making the variation in the storage capacity of the capacitor even smaller without the growth of a natural oxide film between the polysilicon gate electrode wiring and the  $\text{Si}_3\text{N}_4$  capacitor insulating film. In this way, using the film forming or etching device according to the present invention makes it possible to increase the storage capacity of the capacitor, which enhances the SN ratio at the time of the DRAM operation and makes it possible to lengthen the refresh time.

(0063)

(EFFECT OF THE INVENTION) With the present invention, the uniformity of film thickness and the uniformity of film quality within the plane of a wafer and between wafers can be enhanced at the time of film formation in a CVD process. In addition, the amounts of the raw material gas and power that are consumed can be reduced.

(BRIEF DESCRIPTION OF THE DRAWINGS)

(FIG. 1) is a horizontal cross-sectional view of a heating furnace of a first example of the present invention when viewed from above.

(FIG. 2) is a vertical cross-sectional view of the heating furnace of the first example of the present invention when viewed from the side.

(FIG. 3) is a perspective view illustrating the division of the heater of the first example of the present invention.

(FIG. 4) is a perspective view illustrating the shape of the reaction tube of the first example of the present invention.

(FIG. 5) is a perspective view illustrating another example of the shape of the reaction tube of the first example of the present invention.

(FIG. 6) is a plan view and a side view illustrating an example

of the structure of the heating furnace of the first example of the present invention.

(FIG. 7) is a system diagram of the gas supply system and the discharge system of the first example of the present invention.

(FIG. 8) is a graph showing the results of calculating the film thickness distribution of a film formed on a wafer when the flow of gas is not switched during film formation in the first example of the present invention.

(FIG. 9) is a graph showing the results of calculating the film thickness distribution of a film formed on a wafer when the flow of gas is switched during film formation in the first example of the present invention.

(FIG. 10) is a cross-sectional view of a vertical CVD device configured to switch the flow of gas during film formation as a second example of the present invention.

(FIG. 11) is a drawing illustrating an example of the method of supplying gas when diffusion is fast in the first example of the present invention.

(FIG. 12) is a graph illustrating an example of changes in temperature of the wafer and the heater in the first example of the present invention.

(FIG. 13) is a graph illustrating an example of changes in temperature of the wafer and the heater when feed forward control is administered in the first example of the present invention.

(FIG. 14) is a graph illustrating an example of the temperature pattern of the back heater during feed forward control in the first example of the present invention.

(FIG. 15) is a graph illustrating an example of the temperature pattern of the central heater during feed forward control in the first example of the present invention.

(FIG. 16) is a graph illustrating an example of the temperature pattern of the front heater during feed forward control in the

first example of the present invention.

(FIG. 17) is a graph illustrating an example of the temperature pattern of the side heaters during feed forward control in the first example of the present invention.

(FIG. 18) is a graph illustrating an example of the temperature control pattern in the case of continuous processing in the first example of the present invention.

(FIG. 19) is a cross-sectional view of an example in which the present invention is applied to a plasma CVD device.

(FIG. 20) is a cross-sectional view of an example in which the present invention is applied to parallel plate type plasma etching device.

(FIG. 21) is a schematic diagram of a DRAM cell with a STC (Stacked Capacitor) structure.

(EXPLANATION OF REFERENCES)

|                               |                             |

|-------------------------------|-----------------------------|

| 1: heater                     | 2: reaction tube            |

| 2a: reinforcing rib           | 3: wafer                    |

| 4a, b, c, d: gas supply ports | 5a, b, c,                   |

| d: discharge ports            |                             |

| 6: SiC plate                  | 7: heat-insulating material |

| 8: support plate              | 9a, b: flanges              |

| 10a, b: gate valves           | 11: fork                    |

| 12: heat-insulating plate     | 13: fixing hardware         |

| 14: throat                    | 15: gas source              |

| 16: vacuum pump               | 17a, b,                     |

| c, d: valves                  |                             |

| 18: cap                       | 21: reinforcing plate       |

| 21a: protrusion               | 22: fixing block            |

| 23: pressure sensor           | 24: gas controller          |

| 25: susceptor                 | 26: reaction chamber        |

| 27: upper electrode           | 28: lower electrode         |

| 29: cooling medium channel    |                             |

(FIG. 1)

(FIG. 2)

(FIG. 3)

(FIG. 4)

(FIG. 8)

(FIG. 5)

(FIG. 6)

(FIG. 10)

(FIG. 7)

(FIG. 11)

(FIG. 9)

(FIG. 12)

(FIG. 13)

(FIG. 14)

(FIG. 18)

(FIG. 15)

(FIG. 16)

(FIG. 17)

(FIG. 21)

STRUCTURE OF STC (Stacked Capacitor)-DRAM

(FIG. 19)

(FIG. 20)

---

Continued from the front page

(72) Inventor Toshiyuki UCHINO

% Musashi Works, Hitachi, Ltd., 5-20-1

Josuihonmachi, Kodaira-shi, Tokyo-to

(72) Inventor Hiroyo NISHIUCHI

% Musashi Works, Hitachi, Ltd., 5-20-1

Josuihonmachi, Kodaira-shi, Tokyo-to

(72) Inventor Atsushi FUJISAWA

% Musashi Works, Hitachi, Ltd., 5-20-1

Josuihonmachi, Kodaira-shi, Tokyo-to

(19)日本国特許庁 (J P)

(12) 公開特許公報 (A)

(11)特許出願公開番号

特開平7-94419

(43)公開日 平成7年(1995)4月7日

(51)Int.Cl.<sup>6</sup>

識別記号

庁内整理番号

F I

技術表示箇所

H 01 L 21/205

21/3065

H 01 L 21/ 302

B

審査請求 未請求 請求項の数15 O L (全 15 頁)

(21)出願番号

特願平5-232994

(22)出願日

平成5年(1993)9月20日

(71)出願人 000005108

株式会社日立製作所

東京都千代田区神田駿河台四丁目6番地

(72)発明者 渡辺 智司

茨城県土浦市神立町502番地 株式会社日立製作所機械研究所内

(72)発明者 平沢 茂樹

茨城県土浦市神立町502番地 株式会社日立製作所機械研究所内

(72)発明者 三瀬 信行

茨城県土浦市神立町502番地 株式会社日立製作所機械研究所内

(74)代理人 弁理士 鵜沼 辰之

最終頁に続く

(54)【発明の名称】 半導体処理装置

(57)【要約】

【目的】 成膜装置あるいはエッチング装置において均一で再現性のよい処理を可能にする。

【構成】 2枚の平行平板ヒーター1により形成される加熱空間内に偏平な反応管2を設け、その内部に処理対象のウエハ3を支持するウエハ3より大きい矩形の支持板8を配置し、反応管2の両端にガス供給口4と排気口5とをそれぞれ設け、反応管2内を流れるガスの流れ方向を切り換える成膜装置。

## 【特許請求の範囲】

【請求項1】 加熱炉内部に反応管を収納し、該反応管の内部に半導体ウエハを収納して加熱し、該反応管内を排気しながらガスを供給してウエハ表面への薄膜の形成または、エピタキシャル成長を行う半導体処理装置において、該加熱炉および該反応管が概略偏平な形状であって、前記反応管は同時に1枚乃至2枚のウエハを概略水平に保持して処理するものであることを特徴とする半導体処理装置。

【請求項2】 請求項1記載の半導体処理装置において、反応管が石英製であることを特徴とする半導体処理装置。

【請求項3】 請求項2記載の半導体処理装置において、反応管の内側または外側あるいは両側に、補強部材を設けたことを特徴とする半導体処理装置。

【請求項4】 請求項3記載の半導体処理装置において、補強部材は反応管に溶接により固定されていることを特徴とする半導体処理装置。

【請求項5】 請求項1記載の半導体処理装置において、加熱炉は複数に分割され処理されるウエハの上下方向に該ウエハの被処理面とほぼ平行に配置した平行平板ヒータを含んでなり、該平行平板ヒータが1つの中心ヒータと、それを囲む複数の周辺ヒータに分割されていることを特徴とする半導体処理装置。

【請求項6】 請求項1記載の半導体処理装置において、ウエハの1回の処理サイクル中、あるいは各サイクル毎に加熱炉の設定温度を変更する手段を含んでなることを特徴とする半導体処理装置。

【請求項7】 加熱炉内部に反応管を収納し、該反応管の内部に半導体ウエハを収納して加熱し、該反応管内を排気しながらガスを供給してウエハ表面への薄膜の形成や、エピタキシャル成長を行う半導体処理装置において、加熱炉が少なくとも2つの構成要素に分割できることを特徴とする半導体処理装置。

【請求項8】 反応室内部にウエハを収納し、反応室内を排気しながらガスを供給しつつ収納されたウエハを加熱あるいは冷却してウエハ表面への薄膜の形成、エピタキシャル成長、エッチングを行う半導体処理装置において、該反応室は収納されたウエハを挟んで互いに対向する位置に少なくとも2個の開口部を有し、各開口部はそれぞれガス供給口と排気口とを有し、該ガス供給口および排気口が各々バルブを介してガス源および真空ポンプに接続され、ウエハ加熱手段あるいは冷却手段を含む反応室の構造およびウエハの位置が、反応室の中心に位置し前記二つの開口部を結ぶ線に垂直な面に対して概略対称になっていることを特徴とする半導体処理装置。

【請求項9】 請求項8記載の半導体処理装置において、同じ開口部に接続されたガス供給口と排気口は、該ガス供給口から供給されたガスのほとんどが反応室を経由することなく排気口に直接流れ出すようにガス供給口

と排気口が近接して配置されていることを特徴とする半導体処理装置

【請求項10】 請求項8記載の半導体処理装置において、処理の途中で反応室のガスの流れ方向を切り替える手段を有することを特徴とする半導体処理装置。

【請求項11】 請求項10記載の半導体処理装置において、反応室のガスの流れ方向を切り替える手段は、ガスの流れを切り替える際に、まず排気口を一方の開口部の排気口から他方の開口部の排気口へ徐々に切り替え、これに続いてガス供給口を該他方の開口部のガス供給口から前記一方の開口部のガス供給口へ徐々に切り替えるものであることを特徴とする半導体処理装置。

【請求項12】 請求項10又は11記載の半導体処理装置において、反応室のガスの流れ方向を切り替える手段は、処理の途中でガスの流れ方向を切り替える際に、反応室の圧力を一定に保つようにガス流量および排気速度を制御するものであることを特徴とする半導体処理装置。

【請求項13】 請求項1乃至第12のいずれかに記載の半導体処理装置において、反応室内に導入したガスがウエハの被処理面とほぼ平行に流れることを特徴とする半導体処理装置。

【請求項14】 請求項1乃至13のいずれかに記載の半導体処理装置において、反応室内に、概略矩形でその各辺が少なくとも収納されるウエハの直径より大きいウエハ保持用の支持板が配置されていることを特徴とする半導体処理装置。

【請求項15】 請求第1～14項記載の半導体処理装置を用いて、ゲート電極配線のポリシリコン膜あるいはリンドープポリシリコン膜、層間絶縁膜のリングラス膜、キャパシタ絶縁膜のSi<sub>3</sub>N<sub>4</sub>膜を成膜することにより製作されたLSI。

## 【発明の詳細な説明】

## 【0001】

【産業上の利用分野】本発明は、半導体製造プロセスにおいて、ウエハ基板表面に金属膜、金属シリサイド膜、酸化膜、窒化膜、あるいは不純物などをドープしたシリコン膜などの薄膜を形成する熱CVD装置、プラズマCVD装置、ウエハ基板上に単結晶層を成長させるエピタキシャル成長装置、薄膜を所定のパターンにエッチングするドライエッチング装置等の半導体処理装置に係り、特にガス供給とウエハ加熱に配慮した半導体処理装置に関する。

## 【0002】

【従来の技術】熱CVD、プラズマCVDによって形成される薄膜およびエピタキシャル成長層の厚さや特性は、ウエハや反応室の温度、ガス（原料ガス、反応生成物、中間体、ラジカルなど）の濃度に大きく依存している。また、ドライエッチングでは、エッチングガスをプラズマで分解して得られるラジカルや反応生成物の濃度

がエッティング速度に大きな影響を与える。このため、ウエハ温度の均一化とガス濃度の均一化がこれらのプロセスの重要な課題になっている。以下、熱CVD装置を主として従来技術を説明する。

【0003】熱CVD装置はバッチ式と枚葉式に大別できる。バッチ式の縦形CVD装置は、縦形の円筒加熱炉内に設けた反応管の内部に水平に保持した多数枚のウエハを挿入し、ガスを供給して膜を生成するホットウォール式装置（反応室の壁面全体が高温になる装置）である。通常ガスを反応管の下部から供給するため、ガスが上方に流れる間に反応が進んでガス濃度が変化し上下のウエハ間に膜厚の差ができるので、加熱炉内に温度勾配をつけてその影響を補正していた。また例えば、特開平4-343412号公報には成膜の途中で反応管内を下から上に流していたガスの流れ方向を上から下に切り換えるようにした技術が開示されているし、特開昭63-8299号公報には、平行平板ヒータで構成された加熱炉内にウェハを垂直に保持して処理する技術が示されている。さらに、特開昭63-232422号公報には、縦型の円筒炉内にウェハを水平に挿入して加熱する拡散装置が示されている。

【0004】枚葉熱CVD装置は水冷された反応室の中で、ランプによって直接ウエハを加熱するか、ヒータあるいはランプ等で加熱されたサセプタ上にウエハを載せて加熱し、ガスを供給して膜を生成するコールドウォール式の装置である。バッチ式と異なりガスの濃度変化によるウエハ間の膜厚ばらつきはないが、ウエハ面内の膜厚分布を低減するため、ウエハを回転させたり、ウエハ上部からシャワー状にガスを供給するといった方法が用いられていた。また例えば、特開平4-255214号公報には、加熱用ランプの形状及び配列を工夫することによりウェハ温度を均一にする技術が示されている。

【0005】プラズマCVD装置は、サセプタ加熱の熱CVD装置と基本的に同じ構造であり、さらにプラズマを発生させるために上部電極が設けられている。ガスの供給方法には、反応室の側壁に設けた複数の導入口からウエハ中心に向けて供給する方法、上部電極に多数の小さな穴を設けてここからシャワー状にガスを供給する方法があった。また、特開昭63-102312号公報には、ウェハとサセプタの間にHeガスを一定圧力で供給することによりウェハ温度の変動を防止する技術が示されている。

【0006】ドライエッティング装置は、大きく平行平板形プラズマエッティング装置とマイクロ波エッティング装置に分けられる。平行平板形プラズマエッティング装置は、プラズマCVD装置のウエハ加熱機構が冷却機構に置き換わった装置で供給するガスが異なるだけである。マイクロ波エッティング装置は、平行平板形プラズマエッティング装置から上部電極を取り去り、ここからマイクロ波を導入するための導波管が設けられている。エッティングガ

スはエッティング室の側面に設けられた複数の導入口からウエハ中心に向けて供給されることが多い。

#### 【0007】

【発明が解決しようとする課題】これら従来技術による装置には、以下のような問題があった。

【0008】バッチ式の縦形CVD装置で、加熱炉内に温度勾配をつけてウエハ間の膜厚ばらつきを低減する方法は、何度も試行錯誤を繰り返し最適な炉内温度分布を見つける作業が必要であり、さらに通常のヒータ分割（現状の装置では4ゾーン）では十分に満足できる温度分布が得られない場合があった。これを解決するため、成膜の途中でガスの流れを逆向きに切り替える方法（特開平4-343412号公報参照）が考案されていたが、加熱炉、反応管の構造、およびウエハの位置などがガス流れに対して対称ではないので、ガスの切り替えだけでは上下のウエハの膜厚ばらつきを十分に低減することが難しかった。

【0009】コールドウォール式の枚葉熱CVD装置（ランプ加熱、サセプタ加熱いずれも）では、ウエハに対して加熱源の温度をかなり高く設定する必要があるので（熱非平衡状態）、ウエハの放射率が変わると（表面に形成された膜の種類や厚さ、あるいは不純物濃度の違いによって、波長に対する特性が変化する。）温度再現性が悪くなるという問題があった。これを解決するため、放射温度計を使ってウエハ温度を直接測定し加熱量を制御する方法が考案されていたが、ウエハ表面に膜が形成されることによって放射率が変化するため、大きな測定誤差が生じ実用的ではなかった。さらに、サセプタ加熱では介在するガスを通じてサセプタからウエハに熱が伝わるため、反応室の圧力やガスの種類、ウエハとサセプタの隙間などによって伝熱量が変わりウエハ温度が変化するという問題があった。この問題を解決するため、ウエハとサセプタの間にHeガスを一定圧力で供給する方法（特開昭63-102312号公報参照）が考案されていたが、ウエハが浮き上がらないように周辺を押さえる必要があるため、それによってウエハ周辺の温度が下がるという問題があった。また、ランプ加熱、サセプタ加熱の装置は消費電力が大きいという問題があった。これに対しコールドウォール式装置の欠点を解消するものとして、縦形角形炉内に垂直に保持したウエハを挿入して加熱する装置（特開昭63-8299号公報参照）、縦形円筒炉内にウエハを水平に挿入して加熱する装置（特開昭63-232422号公報参照）が考案されていた（いずれもホットウォール式装置）。しかし、ウエハを支える石英治具が温まりにくいため、ウエハ面内で治具が接触する部分の温度上昇が遅くなり、温度均一性が悪くなるという問題があった。さらに、ハンドリングの問題からマルチチャンバへの対応が困難であった。

【0010】プラズマCVD装置、ドライエッティング装

置において、反応室側壁の複数の導入口からウエハ中心に向けてガスを供給する方式では、ウエハ中心に反応生成物などが滞留しやすいため、膜厚やエッティング速度の不均一を生じやすかった。一方、上部電極の穴からシャワー状に供給する装置では、穴の付近でプラズマが異常放電をすることがあった。また、穴の近傍に反応生成物が付着しやすく、異物の発生原因になるという問題があった。

【0011】本発明の目的は、成膜装置あるいはエッティング装置において均一なガス濃度および均一なウエハ温度および温度再現性が得られる装置構造を与え、均一で再現性の良い処理を可能にすることにある。

#### 【0012】

【課題を解決するための手段】上記の目的は、熱CVD装置において抵抗加熱によるホットウォール式の枚葉式装置を実現することにより達せられる。具体的には、加熱炉を偏平な形状とし、この加熱炉内に同様に偏平な反応容器を入れ、この反応容器の内部に1枚乃至2枚のウエハを水平に挿入して加熱するとともに、反応容器内にガスを供給してウエハ表面に膜を堆積させることによって達成される。さらに、その各辺がウエハ直径より大きい矩形支持板にウエハを載せて処理することにより達成される。また、反応容器に少なくとも2つの開口部を設け、この開口部に少なくとも2組のガス供給口および排気口を設け、成膜の途中でガスの流れを切り替えて成膜することにより達成される。

【0013】一方、プラズマCVD装置、ドライエッティング装置において反応室に少なくとも2組のガス供給口と排気口とを設け、供給したガスがウエハ上を一方向に流れるようにし、成膜あるいはエッティングの途中でガスの流れ方向を切り替えて処理を進めることにより達成される。

#### 【0014】

【作用】熱CVD装置において、

・ホットウォール式であるため、ウエハと加熱炉内壁が熱平衡状態（両者の温度が等しい状態）になり、膜の種類や厚さによらずウエハ温度が一定に保たれ温度再現性が向上する。

【0015】・加熱炉が偏平形状で開口部からの放熱を低減できるため、小形の加熱炉でもウエハ面内の温度均一性がよい。これにより、ウエハを加熱炉内に挿入あるいは引き出すためのハンドリング機構を小型化できる。

【0016】・成膜の途中でガスの流れ方向を切り替えることにより、流れに沿った濃度変化によって生ずるウエハ面内の膜厚分布を低減できる。特に、加熱炉の中心に位置しガスの流れ（反応室のウエハを挟んで互いに対向する開口部を結ぶ線）に垂直な面に対して、反応管、ガス流路および加熱炉の構造が概略対称になっているため、前半と後半の膜厚分布が対称となり、結果として膜厚の均一性が非常に良くなる。

【0017】・矩形支持板の各辺がウエハ直径より大きいため、ウエハ周辺で膜厚が厚くなるのを防ぐことができる。また、形状が矩形であるため、ガスの流れに垂直方向のウエハ面内の膜厚分布を小さくすることができる。

【0018】・矩形支持板を常に加熱炉内に入れっぱなしにし、加熱炉内に挿入したウエハをこの支持板に移載して処理するので、ウエハが迅速に温度上昇し温度が均一になり易い。

【0019】・ウエハを概略水平に保持し、水平方向に移動させて加熱炉内に挿入する構造であるため、ハンドリングが簡単で、マルチチャンバ方式への対応が容易になる。また、プラズマCVD装置、ドライエッティング装置において、

・ウエハ表面をガスが一方向に流れるため、反応生成物を速やかに排気できる。このため、ウエハ中央に反応生成物が滞留することがなくなる。

【0020】・ガス導入口および排気口を途中で切り替えガスの流れ方向を変えて処理することにより、ウエハを回転させるのと同じ効果をより簡単に得られ、膜厚あるいはエッティング量の均一化が達成できる。

【0021】・上部電極にガスを流す穴をあける必要がないため電極の構造が単純になり、プラズマ異常放電が起きにくく。

#### 【0022】

【実施例】以下、本発明の第1の実施例を図を用いて説明する。図1は本発明を適用したCVD装置の加熱炉を上方から見た断面平面図、図2は加熱炉を側方から見た断面図である。図示のCVD装置は、軸線をほぼ水平にして配置され両端が開放された扁平な反応管2と、該反応管2の内部にほぼ水平に上下2層に配置された矩形の支持板8と、該反応管2の上下に反応管2を挟んで対向して配置され加熱炉を形成する平板状のヒータ1と、前記反応管2の両端に結合されたフランジ9a, bと、該フランジ9a, bの肉厚内に前記反応管2の軸線と垂直方向にかつ中心から図上上方に向かって形成されたガス供給口4a, bと、同じくフランジ9a, bの中心から図上上方に向かって形成された排気口5a, bと、前記ヒータ1の外側に設けられた断熱材7と、前記フランジ9a, bの外側に結合され該フランジ9a, bの中心開口に当面するゲートバルブ10a, bと、を含んで構成されている。

【0023】本装置では、反応管2の中にウエハ3が水平状態で挿入され、支持板8に載置される。載置されたウエハ3はヒータ1により加熱され、同時にガス供給口4a, bのいずれかからガスを供給しながら、同じく反応管2の両端に形成された排気口5a, bのいずれか（ガスが供給される側とウエハ3を挟んで反対側）から排気してウエハ3の表面に膜を生成したり、エピタキシャル成長を行う。支持板8は、上下2段に設けられており、各

支持板8にはそれぞれ1枚のウェハが載置されるようになっていて、ウェハ3は1枚あるいは2枚同時に処理される。ガスはウェハ3の表面にほぼ平行に流れる。ヒータ1は複数に分割され、ウェハ3の温度分布が均一になるように各々発熱量が調整される。ヒータ1の外側には断熱材7が設けられ、周囲への放熱を減らし消費電力を低減するように考慮されている。

【0024】反応管2の両端にはフランジ9a、bを介してゲートバルブ10a、bが設けられ、ウェハ3は一方のゲートバルブ10aを開いた状態で該ゲートバルブ10aを通してフォーク11に載せられて反応管2の内部に挿入される。挿入されたウェハ3はフォーク11から支持板8に移し換えられ、フォーク11を引き抜いた後ゲートバルブ10aが閉じられてガスが流れ、成膜が行われる。なお、支持板8はフォーク11の動作範囲を切り欠いてある。

【0025】本実施例のようにウェハを2枚同時に処理する場合は、支持板8は透明な石英製が望ましい。ウェハを同時に1枚処理する場合はシリコン製、SiC製、SiCあるいはポリシリコンがコーティングされた石英製などの不透明な材質でもよい。支持板8の下側には少なくとも3個の脚8a(図示せず)が、フォーク11の動作範囲に干渉しない位置で、かつできるだけウェハ3から離れた位置に設けられる。ウェハを同時に2枚処理するときは、下の支持板8を反応管2の下側壁の内面に置き、その上に上の支持板8を置く。上下の支持板8は一体物として製作してもよい。また、上下のウェハの膜厚を等しくするには(温度が同じだと仮定して)、上側ウェハ3の表面から反応管2上壁内面までの距離と、下側ウェハ3の表面から上側支持板8の下の面までの距離を等しくすることが重要である。これは、ウェハ3の表面に形成される膜の成長速度が、膜が成長する面の面積とその周囲のガスが反応する空間の体積の比に依存するからである。したがって、支持板8の脚8aの長さは、この条件が満たされる長さとなっている。

【0026】また、支持板8と反応管2の材質は同じにする方が望ましい(表面が同じ材質であればよい)。これは、材質によっては他の条件が同じでも成膜速度が異なる場合があるからで、支持板8と反応管2への成膜速度が異なれば、その付近の気体中のガス濃度が変わるから、結果として上下のウェハで成膜速度が変わってしまうことになる。

【0027】図3にヒータ1の分割例を示す。図示の例ではヒータ1は、ウェハの中心に対面するCヒータと、この手前側(ウェハを挿入する側)のFヒータと、奥側のBヒータと、Cヒータの両サイドのSヒータから構成される。F、Bヒータは反応管2の両側に設けられた開口部からの放熱を補うために、Cヒータより発熱密度を高くしてある。また、両サイドのSヒータは、Cヒータよりは高く、F、Bヒータよりは低い発熱密度にしてあ

る。中央部のCヒータは概略ウェハと同じ大きさにすることが望ましい。

【0028】図4に反応管形状の一例を示す。成膜中は反応管2の内部は数Torr以下に減圧されるため、反応管2は1気圧の外圧に耐えられなければならない。本実施例のCVD装置で径200mmのウェハ3を2枚同時に処理する場合、反応管2の内部寸法として幅300mm×奥行き500mm×高さ40mm程度の大きさが必要となる。反応管2は石英で製作されることが多いが、この大きさで1気圧の外圧に耐えるには、反応管2の厚さは少なくとも10mm以上必要である。しかも、10mmの厚さでは、側面中央に石英の引張強度とほぼ同じ引張応力が生ずるため安全率が1となり、製作時に欠陥があれば破損する恐れが高い。バッチ式と同程度の強度(バッチ式の縦形CVD装置では反応管の形状を円筒状にできるため、4~6mm程度の厚さで安全率3~5程度の強度が容易に得られる)を得るには、反応管2の厚さを20mm以上にしなければならなかった。しかし、このような厚い石英板を溶接して反応管2を製作することは実現困難であった。本実施例の反応管2は図4に示すように外側に一定間隔で石英の補強リブ2aを環状に設け、石英製の反応管本体に溶接したものである。このような構造にすることによって、反応管2の側面に生ずる応力を低減できる。

【0029】図5に反応管2の内側に石英の補強板21を入れた他の実施例を示す。補強板21は石英の他、SiC、Si等の耐熱性材料で作ってもよい。補強板21は平板状に形成され、その両端はフランジ9a、bに固定ブロック22で固定され、補強板21の反応管内面に対向する面に設けた突起21aが、反応管2の内面中央部に接触するように反応管内面に平行に保持される。補強板21の厚さは使用する材料によって適当な厚さが選ばれる。外圧によって反応管2に生ずるたわみは中央部が最も大きくなるため、ここを補強板21で支持することで反応管2の側面に生ずる応力を低減できる。

【0030】本発明の一つの要点である加熱炉を偏平な形状にする理由は、それによって開口部を小さくして放熱を低減し、小さな加熱炉でもウェハ3の温度を均一にできるからである。ここで、図1及び図2に示すCVD装置において、炉内長(ウェハの挿入方向に対して断熱材の内側から内側までの長さ)と開口部の高さの比が少なくともより大きくなる程度に開口部の高さを低くした偏平形状が望ましい。次に、開口部の高さを低くするための加熱炉構造について説明する。図6は本発明の加熱炉の構造を示す外形図である。一体型の加熱炉の場合、図4および5に示した反応管2を炉内に入れるためには、少なくとも補強リブが通る大きさの開口部が必要である。しかし、図6に示すように加熱炉を複数に分割することによって、開口部を補強リブより小さくすることができる。図6の(a)に示す実施例はヒータ1から

なる加熱炉本体と、その軸方向両端に付けた断熱板12から構成されており、断熱板12は上下に2分割されている。反応管2は断熱板12をはずした状態で炉内に挿入され、そのあとで断熱板12が加熱炉本体1に固定金具13により取り付けられる。上下の断熱板12の隙間

(炉口14)は、補強リブ2aを除いた反応管2本体が通る大きさにしてある。断熱板12は固定金具13により加熱炉本体に脱着可能に取り付けられる。図6(b)は加熱炉本体が上下に2分割され、上側ヒータをはずし下側ヒータに反応管2を設置し、上から上側ヒータをかぶせて加熱炉を構成するようにした例である。

【0031】図7は図1に示した実施例のガス供給系と、排気系の系統図である。反応管2の軸方向両側にフランジ9a、bを設け、フランジ9aにガス供給口4aと排気口5aが、フランジ9bにガス供給口4bと排気口5bが、それぞれ取り付けられている。ガス供給口4a、bはバルブ17a、bを通してガス源15に、排気口5a、bはバルブ17c、dを通して真空ポンプ16に各々接続されている。ウエハ3は反応管2の中に挿入して加熱され、ウエハ3が所定の温度に達した後で所定時間ガスが流されて成膜が行われる。

【0032】成膜の前半では、バルブ17a、17dを開け、バルブ17b、17cを閉じてガスが供給される。この時は反応ガスは図中の黒い矢印のように反応管2内を左から右に流れる。成膜の前半が終了したら次に、バルブ17aおよび17dが閉じられ、バルブ17b、17cが開かれる。その時、ガスは図中の白い矢印のように反応管2内を右から左に流れる。

【0033】成膜時間を短くするという点からは、バルブ17a、b、c、dの開閉切り替えを短時間で行う方が望ましいが、反応管2内の圧力およびガスの流れが急激に変化して反応管2の開口部付近に付着した反応生成物が剥離するなどの問題が生ずる場合もある。この場合には以下の手順でガスを切り替える。

【0034】(1) 排気口5aを徐々に閉じ、排気口5bを徐々に開ける。

【0035】(2) 排気口5aが完全に閉じ、排気口5bが完全に開いたら、ガス供給口4aを徐々に開け、ガス供給口4bを徐々に閉じる。

【0036】(3) この間、圧力センサ23で反応管2内の圧力を測定し、ガスコントローラ24は反応管2内の圧力が一定になるようにバルブ17a、b、c、dの開度を調整する。

【0037】反応管内のガスの流れ方向を切り替えない場合の、ウエハに形成される膜の成膜速度分布を図8に示す。NH<sub>3</sub>とSiH<sub>2</sub>Cl<sub>2</sub>を用いてSi<sub>3</sub>N<sub>4</sub>膜を付けた場合の、成膜速度分布を計算で求めた結果である。d<sub>x</sub>はガス入り口からガス流れ方向に距離xの位置での膜厚、d<sub>0</sub>はガス入り口での膜厚をそれぞれ示す。ガスの流速を早くして(流量を増やして)、供給したガスの中で反

応で消費される割合を少なくすれば、例えば一点鎖線で示されるように、ほぼ均一な膜厚分布が得られるが、

(1) ガスを多量に消費する。

【0038】(2) ガスでウエハが冷却され面内の温度均一性が損なわれる。

【0039】等の問題がある。

【0040】ガスの流れを途中で切り替えた場合の同様の計算結果を図9に示す。図から成膜の前半と後半の成膜速度分布が重ね合わされることにより、より低いガス流量(流速12.0m/sec)で均一な厚さの膜が得られることがわかる。ここで特に膜厚分布を均一にするのに重要な点は、前半と後半の成膜速度分布を中心位置に対して対称にすることである。これには、装置の構造を対称にし、ガスの流れ、濃度、温度分布等を、ウェハの反応管軸方向中心位置に対して対称にすることが重要である。本実施例に示す枚葉CVD装置では、ヒータ1および反応管2の構造が反応管軸方向中心位置に対して完全に対称になっているため、膜厚の均一性が従来より格段に良くなる。

【0041】ガスの切り替え周期は、仮にウェハ3の温度が定常に達していれば、成膜の前半と後半で切り替えるだけでよい。しかし後述するようにウェハ3の温度が成膜中にも変化していく場合には、より短い周期で切り替える必要がある。

【0042】図10は本発明の第2の実施例を示し、縦形CVD装置において、開口部を2つ有し加熱炉および反応管2の構造を上下対称とした例である。図10に示す実施例は反応管2の上側にも下側と同様に開口部を設け、上側開口部と下側開口部にキャップ18が取り付けられている。ウエハ3は従来の装置と同様に下から挿入され、その下には上側と同じキャップ18が取り付けられる。ヒータは例えば4ゾーン分割とし、中央部の2ゾーンと端の2ゾーンに分け、ウエハの温度分布が上下対称になるようにしている。また、ガスの流れは前半下から上へ流れるようにした場合、後半は上から下へ流れるようにする。構造が上下対称になっているので重力の影響以外は全く上下対称の流れである(低圧プロセスであるため重力の影響は小さい)。これによって先に示した第1の実施例の枚葉CVD装置と同様にウエハ間の膜厚均一性が向上する。

【0043】なお、上記の二つの実施例では反応管2に2つの開口部がある場合について説明したが、開口部が3箇所以上あって適時ガスの供給口および排気口をかえ、ガスの流れ方向を3方向以上に変化させてもよい。例えば、中央にガス供給口4cを設け、このガス供給口4cからガスを供給し、両端の排気口5a、bから排気する工程を前記の2つの工程に加えてもよい。これによってウエハ3中央での膜厚の低下を補正し、さらに膜厚分布を均一にできる。

【0044】また、ガスの拡散が速い場合には、枚葉C

VD装置では図11に示すように、バルブ17a、b、c、dを全て開放し、ガス供給口4a、4bから導入したガスが排気口5a、5bからすぐに排気されるようにし、ウエハ3へは拡散だけでガスが供給されるようにしてもウエハ3面内の膜厚は均一になる。

【0045】さらに、本実施例では図1に示すように支持板8が矩形であるため、ガスの流れ及び流れに沿ったガス濃度の分布がウエハ中央と端（図1では上側あるいは下側）でほぼ同じになる。このため、流れに垂直な断面におけるウエハ面内の膜厚分布が小さくなる。また、先に説明したように、2枚のウエハ3を同時に処理する場合、上側ウエハ3の上面と反応管2の上壁内面と、下側ウエハ3の上面と上側支持板8の下面の間隔を等しくする必要がある。これにより、上下のウエハ3に対するガス流れ及びガス濃度がほぼ同じになり、2枚のウエハの膜厚差を小さくできる。

【0046】次に、ウエハ面内の温度分布を低減する方法について説明する。図1に示す枚葉CVD装置内にウエハ3を挿入した時のウエハの温度（図の（a））と、ヒータの温度（図の（b））およびウエハの中央を基準にした温度差（図の（c））の時間変化を図12に示す（径200mmのウエハを炉内に挿入し、定常状態に達した時点でウエハ温度偏差が所定温度に対し±1°Cの範囲に入るようヒータ設定温度を調整した場合）。ウエハ3の温度は加熱炉内に挿入した直後は急激に上昇し、約1分でほぼ定常温度に達し、さらにこの後徐々に上昇して炉内温度に近づく。ヒータは冷たいウエハ3が挿入されるため一旦温度が下がり、数分間経過した後で元の温度に回復している。ここでウエハ3に直接正対するCヒータの温度低下が最も大きい。これらが原因となってウエハ3は奥および側方の温度上昇が速く、続いて手前、中央と言う順序になる。

【0047】ウエハ3の温度分布を低減するには、中央の温度上昇を速くすることが効果的である。したがって、例えばウエハ3が挿入される時点まで、Cヒータの設定温度を高くしておく、あるいはB、Sヒータの設定温度を低くしておくとよい。このような温度制御を行った場合のウエハ3の温度変化を図13に示す。ウエハ中央の温度上昇が速くなり、成膜を開始する時点でのウエハ面内の温度分布が小さくなっている。

【0048】ここでは各ヒータの設定温度をウエハ3を挿入する時点で切り替える例について述べたが、これ以外の時点でもよく、また1回の処理中に複数回ヒータ設定温度変更を行ってもよい。

【0049】その一例を図14～17に示す（1サイクル=6分30秒）。

【0050】これは、

（1）1枚目のウエハが入る前に設定温度を変更する。（周辺ヒータB、F、Sの温度を下げ、中央ヒータCの温度を上げる。）

（2）ウエハが挿入されてから一定時間経過後設定温度を元に戻す。

【0051】（3）ウエハ引出の一定時間前（2枚目のウエハが入る前）に、1枚目のウエハが入る前と同様に設定温度を変更する。

【0052】（4）上記（1）から（2）の手順を繰り返す。

【0053】という手順（以後、この手順に基づいてヒータ設定温度を変更した場合において、それぞれ設定温度が一定の間をイベントと呼ぶ）からなり、あらかじめ各ヒータの設定温度の変更パターンは決めておく（フィードフォワード制御）。

【0054】また、図12よりウエハを挿入した後、ヒータ温度が定常状態に回復するのに5～6分かかることがわかる。これ以下の時間で処理が繰り返されると、2回目以降の処理では徐々に炉内温度が変化する（多くの場合は下がる。）。このため、処理回数によってヒータの設定温度を徐々に上げ、処理温度の低下を補正する必要がある。この方法の一例を図18に示す。ただし、P(i, j)は第i枚目のウエハに対する処理、第j番目のイベントを指すものとする。

【0055】設定温度の決め方は、

（1）処理n、イベントj-1の終了時点でのヒータ温度T<sub>m</sub>(n, j-1)と、1枚目のウエハの処理の同時点におけるヒータ温度T<sub>m</sub>(1, j-1)の差△T<sub>m</sub>(n, j-1)を求める。

【0056】（2）上記の温度差△T<sub>m</sub>(n, j-1)から適当な係数a(j), b(j)を用いて、次式より補正值△T<sub>set</sub>(n, j)（最終イベントでは△T<sub>set</sub>(n+1, 1)）を求め、これに続くイベントP(n, j)（最終イベントではP(n+1, 1)）の設定温度T<sub>set</sub>(n, j)（最終イベントではT<sub>set</sub>(n+1, 1)）を求める。

【0057】となり、式で表せば

$$T_{set}(n, j) = T_{set}(1, j) + \Delta T_{set}(n, j) = T_{set}(1, j) + a(j) \times \Delta T_m(n, j-1) + b(j)$$

【0058】図18はB（奥側）ヒータに対し第2および第4イベント終了時点で上記の制御を行った例であり、他のヒータについても同様の制御を行えばよい。

【0059】次に、熱CVD装置以外に本発明のガス供給方法を適用した実施例を示す。図19に本発明によるプラズマCVD装置の断面を示す。図示の装置は、両端が閉じられた円筒状をなし軸線を縦にして配置された反応室26と、該反応室26にウェハ載置面を水平にして内装されたサセプタ26と、該サセプタ26のウェハ載置面に電極面を対向させて配置された上部電極27と、該上部電極27の電極面の延長面とサセプタ26のウェハ載置面の延長面が反応室26の壁面と交わる線で挟まれた反応室26の壁面部分に形成された複数の開口と、

該複数の開口それぞれに接続されたガス供給口4 a, b, c, d, …及び排気口5 a, b, c, d, …とを含んで構成されている。サセプタ26のウェハ載置面の下方には、ヒータ1が配置されている。

【0060】上記構成の装置において、ヒータ1を組み込んだサセプタ25の上(ウェハ載置面)にウェハ3を載せてヒータ1で加熱し、反応室26の側壁に設けたガス供給口4 aからガスを供給し、排気口5 bから排気し、上部電極27とウェハ3の間に高周波電圧を供給してプラズマを発生させて、ガスを分解しウェハ3の表面に膜を形成する。成膜の途中でガス供給口4 bからガスを供給し、排気口5 aから排気するようにガスの流れを切り替える。これにより、ウェハ3上のガスの流れにより反応に伴って発生する反応生成物を速やかに排気することができ、さらにウェハ3面内の膜厚分布も小さくできる。さらに、ガスをガス供給口4 cから供給し、手前右側に位置する排気口5 f(図示せず)から排気する行程、ガス供給口4 dから供給し、手前左側に位置する排気口5 e(図示せず)から排気する行程、および各々その反対方向にガスを流す行程を追加してもよく、特にガス供給口および排気口の数を限定するものではない。なお、何らかの理由でホットウォール式のCVD装置が利用できないプロセスには、図10に示すプラズマCVD装置から上部電極27を除いた熱CVD装置を用いれば膜厚の均一化に効果がある。

【0061】図20は本発明による平行平板形プラズマエッティング装置の断面を示す図である。図示の装置は、図19に示した装置のサセプタ26に代えて、上面をウェハ載置面を兼ねる電極面とした下部電極28を設けたもので、該ウェハ載置面下方の下部電極内に、冷媒流路29が形成されている。他の構成は図19に示した装置と同様なので同様の符号を付し、説明は省略する。上記構成の装置において、下部電極28のウェハ載置面(電極面)にウェハ3を載せ、反応室26の側壁に設けたガス供給口4 aからエッティングガスを供給し、排気口5 bから排気し、上部電極27とウェハ3の間に高周波を供給してプラズマ発生させて、エッティングガスを分解しウェハ3の表面に形成された膜をエッティングする。下部電極28に設けられた冷媒流路29に冷媒が流れ、ウェハ3が所定の温度になるように冷却される。エッティングの途中でガス供給口4 bからエッティングを供給し、排気口5 aから排気するようにガスの流れを切り替える。これにより、プラズマCVD装置と同様に反応生成物を速やかに排気でき、ウェハ3面内のエッティング速度の分布も小さくなる。さらに、プラズマCVD装置の実施例で述べたように、これとは異なる方向からガスを流す行程を加えてもよい。

【0062】図21はSTC(Stacked Capacitor)構造のDRAMセルの模式図である。このようなDRAMの製造プロセスにおいて、本発明による熱CVD装置

を用いて形成される膜には、ゲート電極配線に用いられるポリシリコン膜あるいはリンドープポリシリコン膜、層間絶縁膜として用いられるリンガラス膜、キャパシタ絶縁膜として用いられるSi<sub>3</sub>N<sub>4</sub>膜などがある。この中で特に最近膜厚の均一化が必要になっているのはキャパシタの形成行程で、絶縁膜Si<sub>3</sub>N<sub>4</sub>の薄膜化と自然酸化膜を抑制することが重要な課題になっている。本発明による成膜装置、エッティング装置を用いて、このキャパシタの形成行程に対する有効性について説明する。本発明による枚葉熱CVD装置の基本性能として、従来の装置よりウェハ間の温度やガス濃度のばらつきによる膜厚の不均一が小さいため、キャパシタ膜の厚さをより薄く設計しキャパシタの蓄電容量を増やすことができる。さらに、本発明によるCVD装置、エッティング装置を組み合わせてマルチチャンバ装置(複数の処理装置を中央チャンバに接続し、その中に配置されたハンドリングロボットによってウェハを各処理装置に挿入し、成膜やエッティング等の処理を連続して行う装置。ウェハを大気にさらすことなく連続して処理を行える。)を構成し、(1)熱CVD装置で第2層ゲート電極配線のポリシリコンの成膜を行い、(2)エッティング装置で第2層ゲート電極配線を所定のパターンにエッティングし、(3)その上に熱CVD装置でキャパシタ絶縁膜Si<sub>3</sub>N<sub>4</sub>膜の成膜を行い、(4)さらに次の反応室で第3層ゲート電極配線のポリシリコンの成膜を行う、という手順でウェハを大気に触れさせずにキャパシタを形成することにより、ポリシリコンゲート電極配線とキャパシタ絶縁膜Si<sub>3</sub>N<sub>4</sub>の間に自然酸化膜が成長せず、さらにキャパシタの蓄電容量のばらつきを小さくするのに効果的である。このように、本発明による成膜あるいはエッティング装置を用いることにより、キャパシタの蓄電容量を増やすことが可能になり、これによってDRAM動作時のSN比が向上し、かつリフレッシュ時間を長くすることができる。

### 【0063】

【発明の効果】本発明によれば、CVDプロセスにおける成膜時のウェハ面内およびウェハ間の膜厚の均一性、膜質の均一性を向上できる。また、原料ガスおよび電力の消費量を減らすことができる。

### 【図面の簡単な説明】

【図1】本発明の第1の実施例の加熱炉を上方から見た水平断面図である。

【図2】本発明の第1の実施例の加熱炉を側方から見た縦断面図である。

【図3】本発明の第1の実施例のヒータ分割を示す斜視図である。

【図4】本発明の第1の実施例の反応管の形状を示す斜視図である。

【図5】本発明の第1の実施例の反応管の形状の他の例を示す斜視図である。

【図6】本発明の第1の実施例の加熱炉の構造例を示す

平面図及び側面図である。

【図7】本発明の第1の実施例のガス供給系と、排気系の系統図である。

【図8】本発明の第1の実施例においてガスの流れを成膜の途中で切り換えない場合のウエハに形成される膜厚分布を計算した結果を示すグラフである。

【図9】本発明の第1の実施例においてガスの流れを成膜の途中で切り替えた場合のウエハに形成される膜厚分布を計算した結果を示すグラフである。

【図10】本発明の第2の実施例である、ガスの流れを成膜の途中で切り替える縦形CVD装置の断面図である。

【図11】本発明の第1の実施例において拡散が速い場合のガスの供給方法の例を示す図である。

【図12】本発明の第1の実施例におけるウエハおよびヒータの温度変化の例を示すグラフである。

【図13】本発明の第1の実施例においてフィードフォワード制御を行った場合のウエハおよびヒータの温度変化の例を示すグラフである。

【図14】本発明の第1の実施例におけるフィードフォワード制御の奥側ヒータの温度パターン例を示すグラフである。

【図15】本発明の第1の実施例におけるフィードフォワード制御の中央ヒータの温度パターン例を示すグラフである。

【図16】本発明の第1の実施例におけるフィードフォワード制御の手前側ヒータの温度パターン例を示すグラフである。

【図17】本発明の第1の実施例におけるフィードフォワード制御の横側ヒータの温度パターン例を示すグラフ

である。

【図18】本発明の第1の実施例における連続処理の場合の温度制御パターン例を示すグラフである。

【図19】本発明をプラズマCVD装置に適用した実施例の断面図である。

【図20】本発明を平行平板形プラズマエッティング装置に適用した実施例の断面図である。

【図21】STC (Stacked Capacitor) 構造のDRAMセルの模式図である。

#### 【符号の説明】

|                    |                   |

|--------------------|-------------------|

| 1 ヒータ              | 2 反応管             |

| 2 a 補強リブ           | 3 ウエハ             |

| 4 a, b, c, d ガス供給口 | 5 a, b, c, d 排気口  |

| 6 SiC板             | 7 断熱材             |

| 8 支持板              | 9 a, b フランジ       |

| 10 a, b ゲートバルブ     | 11 フォーク           |

| 12 断熱板             | 13 固定金具           |

| 14 炉口              | 15 ガス源            |

| 16 真空ポンプ           | 17 a, b, c, d バルブ |

| 18 キャップ            | 21 補強板            |

| 21 a 突起            | 22 固定プロック         |